Graduate Theses and Dissertations

Graduate School

3-3-2008

# Development of an FPGA Based Autopilot Hardware Platform for Research and Development of Autonomous Systems

Wendy Alvis University of South Florida

Follow this and additional works at: https://scholarcommons.usf.edu/etd

Part of the American Studies Commons

## Scholar Commons Citation

Alvis, Wendy, "Development of an FPGA Based Autopilot Hardware Platform for Research and Development of Autonomous Systems" (2008). Graduate Theses and Dissertations. https://scholarcommons.usf.edu/etd/118

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

# Development of an FPGA Based Autopilot Hardware Platform for Research and Development of Autonomous Systems

by

Wendy Alvis

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Department of Electrical Engineering

College of Engineering

University of South Florida

Co-Major Professor: Wilfrido Moreno, Ph.D. Co-Major Professor: Kimon Valavanis, Ph.D. James T. Leffew, Ph.D. Paris Wiley, Ph.D. Richard Wallace, Ph.D. MaryAnne Fields, Ph.D.

Date of Approval: March 3, 2008

Keywords: Field Programmable Gate Array, unmanned systems, embedded systems, analog design, UGV

© Copyright 2008, Wendy Alvis

#### **DEDICATION**

To God for giving me the strength to get through many sleepless nights, the stubborn nature that kept me from ever giving up on my goals and the gift of surrounding me with such wonderful friends and family who encouraged me along the way.

To the light of my life, my daughter Danielle, who so generously gave up time with her mother in order for me to realize my dream. Her friendship and love is the greatest gift in my life.

To my husband, my one and only true love and my sole-mate Jim, for putting his goals on hold in order to support mine. I could not have completed this dream without his patience, emotional support and financial sacrifices.

To my parents, Jacqueline and Harry Trietley, for always being there to support and help me over the years.

To my grandmother, Marjorie Bechtold, for all her prayers and unconditional love; this gave me the self confidence to succeed.

To my sister and her family, Lisa, Andy and Heather Patterson, their words of friendship and encouragement were always there to bolster me.

#### **ACKNOWLEDGEMENTS**

I thank all the caring and supportive professors that I have had the privilege of working with during my time at the University of South Florida. In particular:

Dr. Leffew; who never turns away a student in need of help,

Dr. Moreno; for all the years as my advisor, encouraging words along the way and late nights revising work completed at the last minute,

Dr. Valavanis; for introducing me to robotics and his support and advice while working on my Ph.D.

I thank the staff of the Army Research Lab for the wonderful summer interning in Maryland, the financial support through a fellowship and their assistance while working on the autopilot. In particular: Dr Wilkerson for making everything possible and Dr Fields for going out of her way to be available for advice and trips to Florida.

I thank my closest friends, Kim Piper, Kim Skinner, Kathy Brown and Shashikala Murthy for their words of encouragement and understanding. An additional thank-you to Shashi for all the hours spent working with me and her excellent work with System Generator.

I thank Xilinx, for their generous contribution of software, Ron, of Advanced Circuits, for the tedious task of assembling the autopilot board and J H Technology, for the use of their equipment and electrical components.

This research was supported in part by an appointment to the Student Research Participation Program at the U.S. Army Research Laboratory administered by the Oak Ridge Institute for Science and Education through an interagency agreement between the U.S. Department of Energy and the US ARL. This work was also partially supported by grant ARO W911NF-06-1-0069 and grant SPAWAR N00039-06-C-0062.

# TABLE OF CONTENTS

| LIST OF TA | ABLES   |                                                      | v    |

|------------|---------|------------------------------------------------------|------|

| LIST OF FI | GURES . |                                                      | vii  |

| ABSTRACT   | Γ       |                                                      | xiii |

| CHAPTER    | 1 INTRO | DDUCTION                                             | 1    |

| CHAPTER 2  | 2 RELA  | TED WORK                                             | 7    |

| 2.1        | Commo   | ercial Autopilots                                    | 7    |

| 2.2        | Related | l State of the Art Research                          | 10   |

|            | 2.2.1   | Microprocessor/DSP Low Power Autopilots              | 11   |

|            | 2.2.2   | Full Computer Implementations.                       | 12   |

|            | 2.2.3   | Implementations Utilizing FPGAs                      | 14   |

| 2.3        | Overvi  | ew of Autopilot Implementations                      | 16   |

| CHAPTER :  | 3 AUTO  | PILOT REQUIREMENTS                                   | 18   |

| CHAPTER 4  | 4 AUTO  | PILOT ENVIRONMENT                                    | 22   |

| 4.1        | Hardwa  | are Overview                                         | 22   |

| 4.2        | Autopi  | lot Software Environment                             | 25   |

|            | 4.2.1   | Hardware Co-Simulation Timing Issues                 | 27   |

|            | 4.2.2   | FPAA Programming and Utilization                     | 30   |

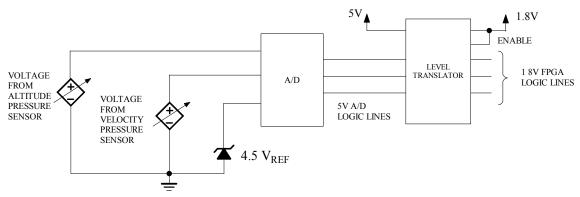

|            | 4.2.3   | Utilizing Pressure Sensors for Altitude and Velocity | 32   |

|            | 4.2.4   | Initializing the MicroSD Card                        | 32   |

|         | 4.2.5 Disabling RS232 Ports                             | 33 |

|---------|---------------------------------------------------------|----|

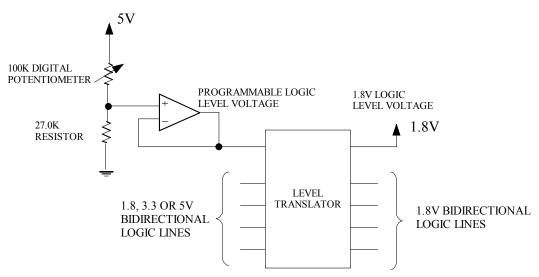

|         | 4.2.6 Setting Variable Voltage I/O Ports                | 34 |

|         | 4.2.7 Utilizing PWM Output Block                        | 34 |

|         | 4.2.8 RS232 Communication Subsystems                    | 36 |

|         | 4.2.9 FPGA RAM Data Acquisition Library Block           | 38 |

|         | 4.2.10 Superstar II GPS Communication Protocol          | 40 |

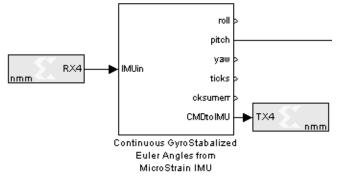

|         | 4.2.11 MicroStrain IMU Communication Protocol           | 41 |

| CHAPTER | 5 HARDWARE DESIGN                                       | 42 |

| 5.1     | Processing Hardware Selection.                          | 42 |

| 5.2     | Analog Input Design                                     | 44 |

| 5.3     | Communication Voltage Level Circuitry                   | 46 |

| 5.4     | Altitude and Velocity Measurement with Pressure Sensors | 48 |

| 5.5     | Data Acquisition Memory                                 | 51 |

| 5.6     | Actuator Control Selector Circuitry                     | 51 |

|         | 5.6.1 Safety Switch CPLD Logic                          | 53 |

| 5.7     | Power Supply Circuitry                                  | 55 |

| CHAPTER | 6 AUTOPILOT SOFTWARE DESIGN                             | 57 |

| 6.1     | FPAA Program Logic Design                               | 60 |

| 6.2     | FPAA Receive Logic Design                               | 62 |

| 6.3     | Pressure Sensor A/D Logic Design.                       | 64 |

| 6.4     | Micro Secure Digital Software Design                    | 69 |

| 6.5     | RS232 Logic Design                                      | 77 |

|         | 6.5.1 RS232 Disable Logic                               | 77 |

|       |       | 6.5.2   | RS232 Send Logic Design               | . 77 |

|-------|-------|---------|---------------------------------------|------|

|       |       | 6.5.3   | RS232 Receive Logic Design            | . 78 |

|       |       | 6.5.4   | RS232 Down-Sample Logic               | . 82 |

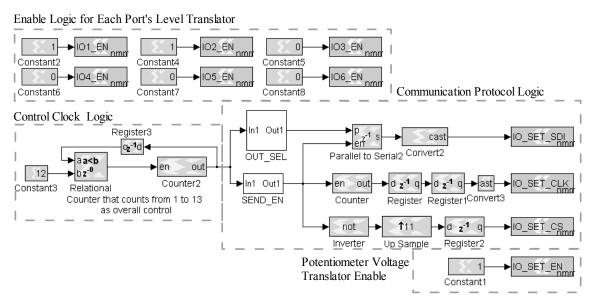

|       | 6.6   | Variabl | e I/O Port Voltage Set Logic          | . 83 |

|       | 6.7   | Servo I | PWM Output Logic                      | . 87 |

|       | 6.8   | FPGA    | RAM Data Acquisition Software Design  | 90   |

|       | 6.9   | GPS U   | nit Communication Protocol            | . 92 |

|       | 6.10  | IMU U   | nit Communication Protocol            | . 96 |

| CHAP  | ΓER 7 | RC-TR   | UCK IMPLEMENTATION                    | . 99 |

|       | 7.1   | RC-Tru  | ick Controller Design.                | 104  |

|       |       | 7.1.1   | ASCII Data Collection                 | 107  |

|       |       | 7.1.2   | Battery Monitoring Design.            | 112  |

|       |       | 7.1.3   | Double and Float Conversion to Binary | 113  |

|       |       | 7.1.4   | Heading Set Point Control.            | 117  |

|       |       | 7.1.5   | Velocity Set Point Control            | 120  |

|       |       | 7.1.6   | Servo Control                         | 121  |

|       | 7.2   | RC-Tru  | ick Results                           | 125  |

| CHAP  | TER 8 | CONC    | LUSIONS                               | 133  |

| REFER | RENC  | ES      |                                       | 135  |

| APPEN | NDICE | ES      |                                       | 140  |

|       | Appe  | ndix A  | Details of Commercial Autopilots      | 141  |

|       | Appe  | ndix B  | Port Connections to the FPGA          | 144  |

| Appendix C Detailed Schematics |          |

|--------------------------------|----------|

| Appendix D Safety Switch Code  |          |

| ABOUT THE AUTHOR               | End Page |

# LIST OF TABLES

| Table 1: Autopilot Specifications                               | 24  |

|-----------------------------------------------------------------|-----|

| Table 2: RS232 Send Input Timing                                | 38  |

| Table 3: Single Switch Truth Table                              | 54  |

| Table 4: RS232 Bit Timing                                       | 79  |

| Table 5: Port Setting Control Counter                           | 85  |

| Table 6: GPS Information Formatting                             | 93  |

| Table 7: Kestral by Procerus                                    | 141 |

| Table 8: MP2028 by Micropilot                                   | 141 |

| Table 9: Ezi-Nav by Autonomous Unmanned Air Vehicles, (AUAV)    | 141 |

| Table 10: Phoenix by O-Navi                                     | 142 |

| Table 11: Piccolo II by Cloudcap                                | 142 |

| Table 12: Microbot by Microbotics                               | 143 |

| Table 13: LED and Switch Port Assignments                       | 144 |

| Table 14: Daughter Board Connector One Safety Switch Connectors | 145 |

| Table 15: Daughter Board Connector One                          | 146 |

| Table 16: Daughter Board Connector Two                          | 147 |

| Table 17: FPAA Connections                                      | 148 |

| Table 18: TTL I/O Ports One to Three Connections                | 149 |

| Table 19: TTL I/O Ports Four to Six Connections                 | 150 |

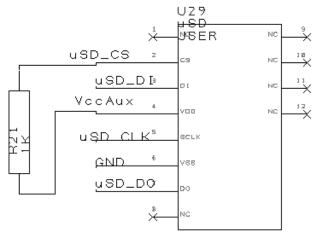

| Table 20: | Flash Memory                | 150 |

|-----------|-----------------------------|-----|

| Table 21: | Pressure Sensor Connections | 151 |

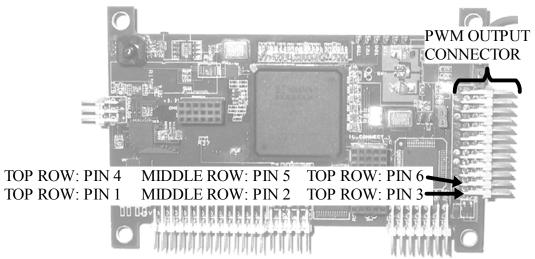

| Table 22: | FPGA PWM Connections        | 151 |

| Table 23: | PWM Output Port Connections | 152 |

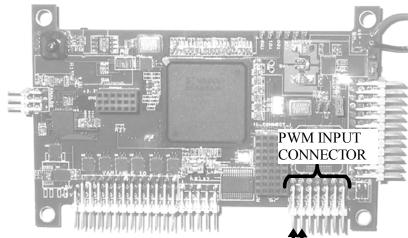

| Table 24: | Pilot Input Connections     | 153 |

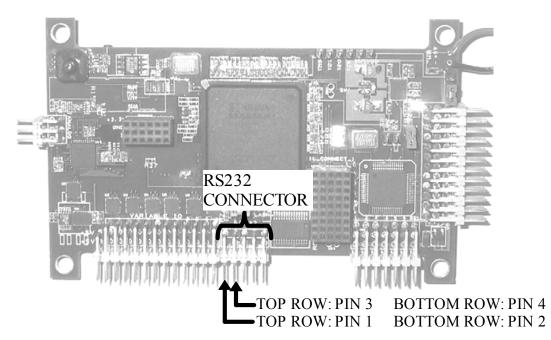

| Table 25  | RS232 Connections           | 154 |

# LIST OF FIGURES

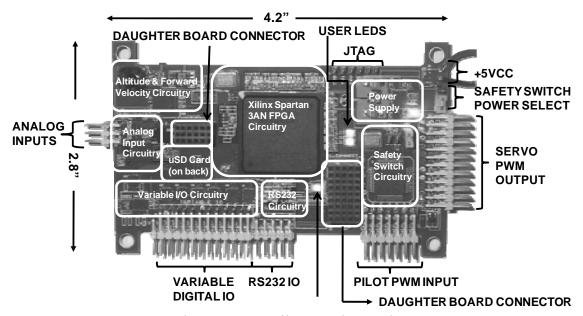

| Figure 1: Autopilot Board Overview                    | 23 |

|-------------------------------------------------------|----|

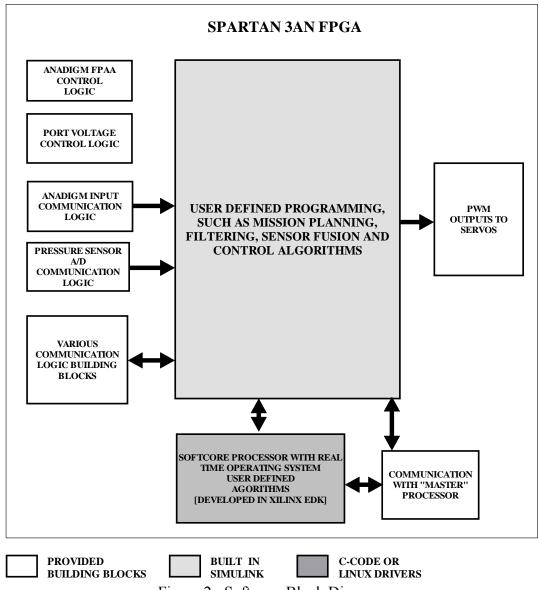

| Figure 2: Software Block Diagram                      | 26 |

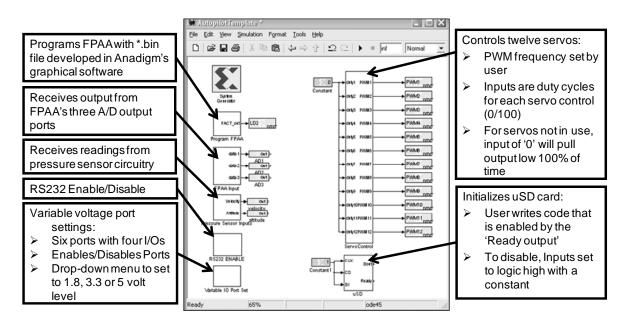

| Figure 3: Autopilot Template                          | 28 |

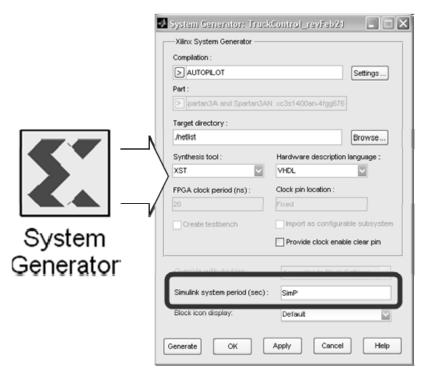

| Figure 4: Simulink System Period Setting              | 30 |

| Figure 5: FPAA Program Settings                       | 31 |

| Figure 6: FPAA Configuration M-File                   | 31 |

| Figure 7: Disabling Pressure Sensor                   | 32 |

| Figure 8: MicroSD Card Template Subsystem             | 33 |

| Figure 9: RS232 Enable                                | 33 |

| Figure 10: Variable I/O Port Settings                 | 34 |

| Figure 11: PWM Subsystem Settings                     | 35 |

| Figure 12: Setting Input Port Timing                  | 37 |

| Figure 13: Setting Baud Rate                          | 37 |

| Figure 14: RS232 Down-Sample                          | 38 |

| Figure 15: Record Data Library Subsystem and Settings | 39 |

| Figure 16: IMU Communication Library Block            | 41 |

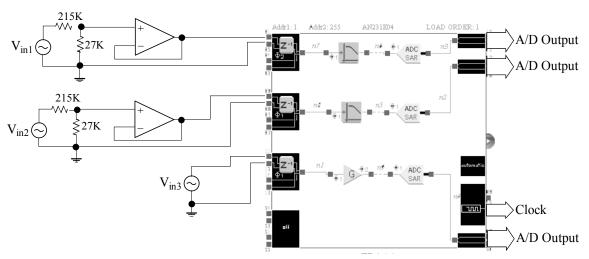

| Figure 17: Voltage Measurement Circuit for Analog     | 46 |

| Figure 18: Adjustable Logic Level Circuitry           | 47 |

| Figure 19: Pressure Sensor Circuitry                  | 49 |

| Figure 20: | Actuator Control                        | . 52 |

|------------|-----------------------------------------|------|

| Figure 21: | Safety Switch Block Diagram             | . 54 |

| Figure 22: | Single Switch Logic                     | . 55 |

| Figure 23: | FPAA Clock Signal                       | 60   |

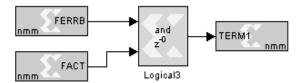

| Figure 24: | Terminating Input Ports                 | 61   |

| Figure 25: | Program FPAA Logic                      | 62   |

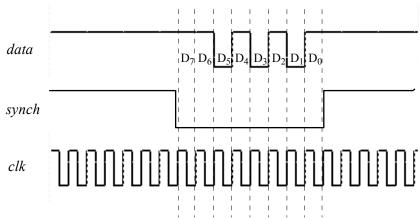

| Figure 26: | FPAA A/D Communication Protocol         | 63   |

| Figure 27: | FPAA Receive Logic.                     | 63   |

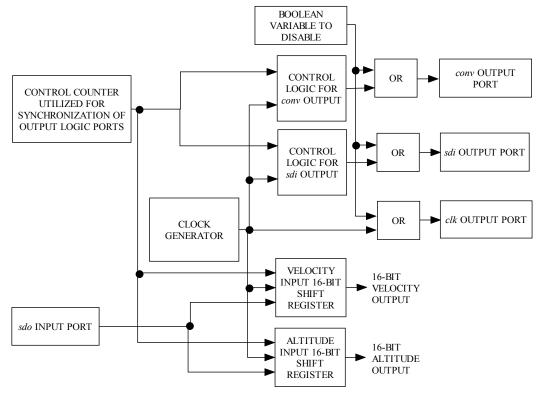

| Figure 28: | A/D Communication Block Diagram         | 65   |

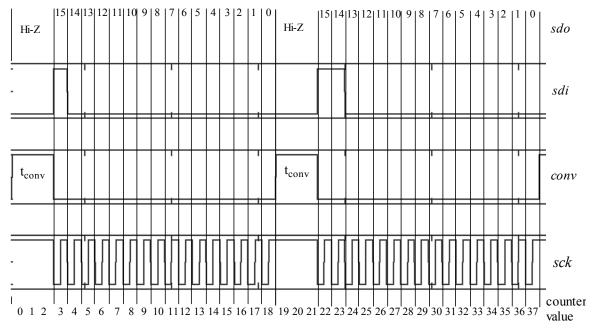

| Figure 29: | A/D Converter Timing                    | . 66 |

| Figure 30: | Logic to Generate Convert Output        | 67   |

| Figure 31: | A/D Clock Generator                     | 67   |

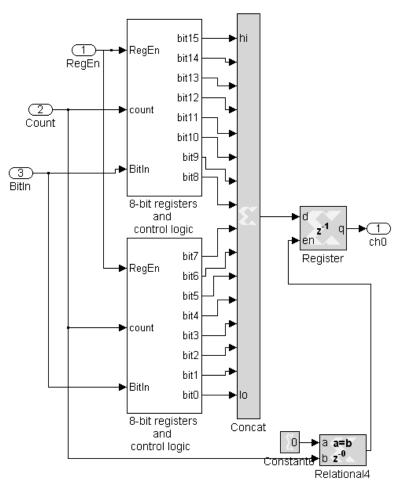

| Figure 32: | Pressure Sensor A/D Input Logic         | 68   |

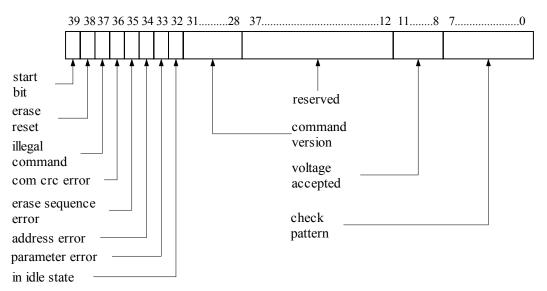

| Figure 33: | MicroSD Card Response                   | . 70 |

| Figure 34: | MicroSD Card Initialization Logic       | . 70 |

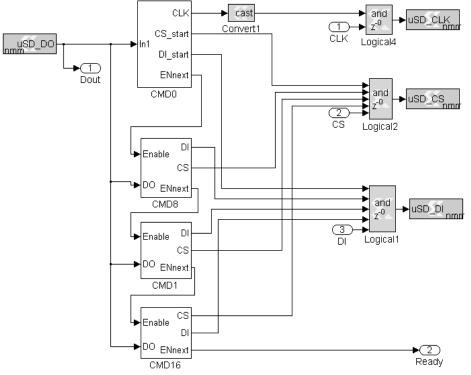

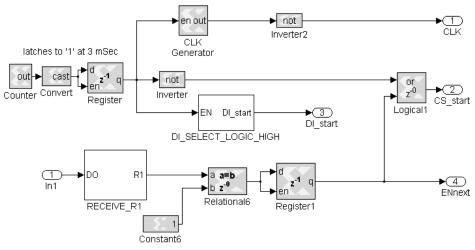

| Figure 35: | CMD0 Subsystem                          | 71   |

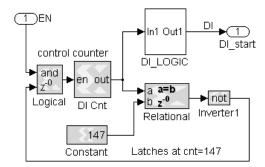

| Figure 36: | CMD0 Logic Output Subsystem             | . 73 |

| Figure 37: | MicroSD Send CMD8 Subsystem             | . 73 |

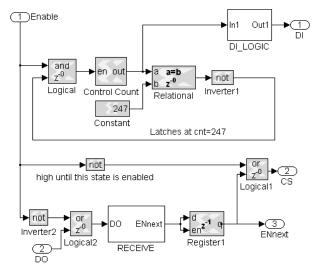

| Figure 38: | MicroSD Receive CMD8 Response Subsystem | . 74 |

| Figure 39: | MicroSD CMD1 Subsystem                  | . 75 |

| Figure 40: | MicroSD CMD16 Subsystem                 | . 76 |

| Figure 41: | RS232 Enable Logic                      | . 77 |

| Figure 42: | Send RS232                              | . 78 |

| Figure 43: | RS232 Receive Diagram                                 | . 78 |

|------------|-------------------------------------------------------|------|

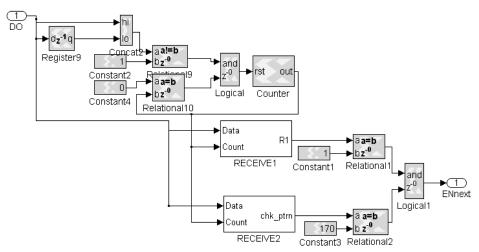

| Figure 44: | RS232 Receive One Byte                                | . 80 |

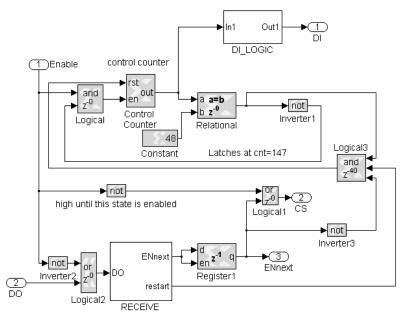

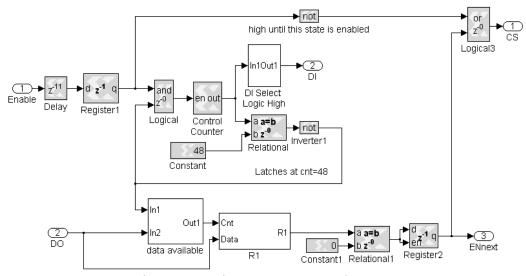

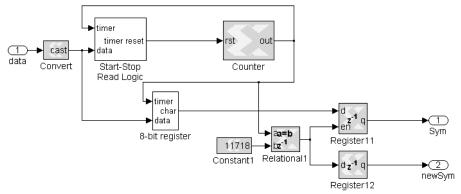

| Figure 45: | RS232 Timer Control Logic                             | . 81 |

| Figure 46: | RS232 Receive Byte Subsystem                          | . 81 |

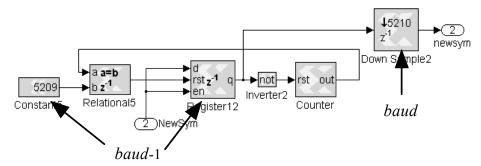

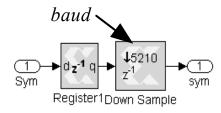

| Figure 47: | Down-Sampling New Bit Logic                           | . 83 |

| Figure 48: | Down-Sampling RS232 Symbol                            | . 83 |

| Figure 49: | Variable Port Voltage Set Subsystem                   | . 84 |

| Figure 50: | Potentiometer SPI Protocol                            | . 85 |

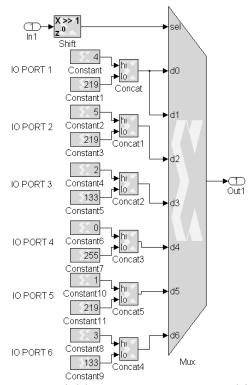

| Figure 51: | Variable Port Data Output Multiplexer                 | . 86 |

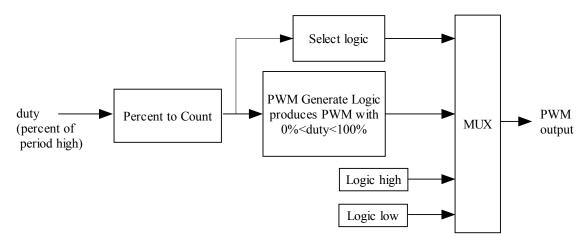

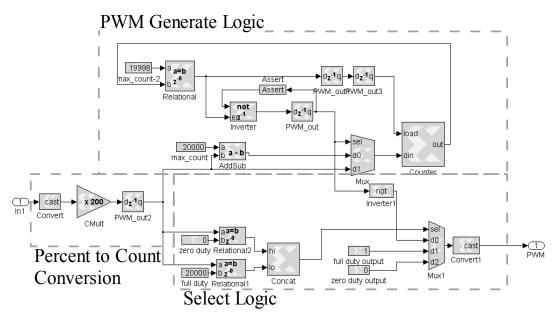

| Figure 52: | PWM Generate Block Diagram                            | . 87 |

| Figure 53: | PWM Generator                                         | . 89 |

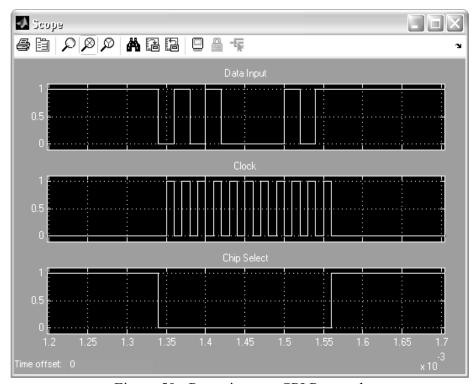

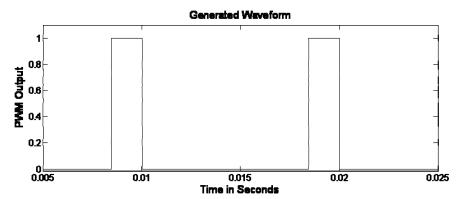

| Figure 54: | Generated PWM Output                                  | . 89 |

| Figure 55: | RAM Data Acquisition Logic                            | . 90 |

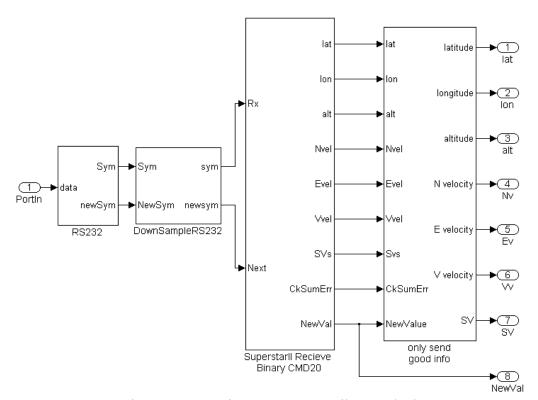

| Figure 56: | Receive Superstar II Library Block                    | . 92 |

| Figure 57: | Superstar II Receive Subsystem                        | . 94 |

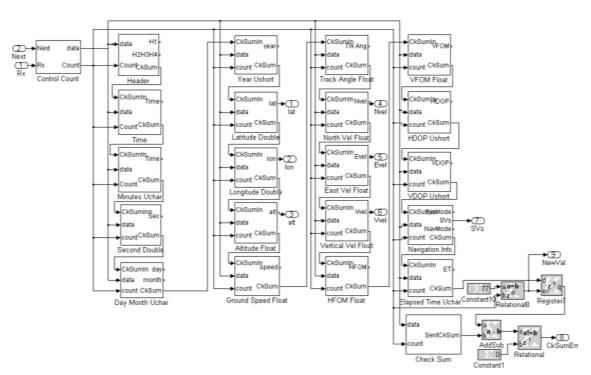

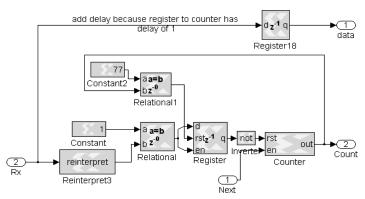

| Figure 58: | GPS Communication Control Counter Subsystem           | . 95 |

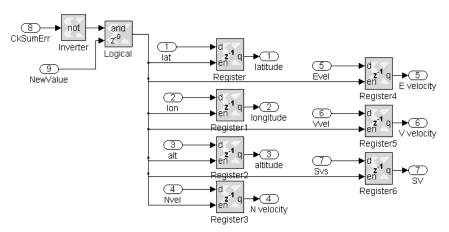

| Figure 59: | GPS Communication Subsystem Update Output Subsystem   | . 95 |

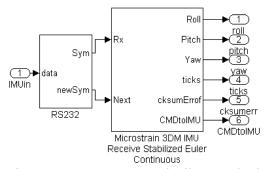

| Figure 60: | IMU Protocol Library Block                            | . 96 |

| Figure 61: | MicroStrain Receive Stabilized Euler Angles Subsystem | . 97 |

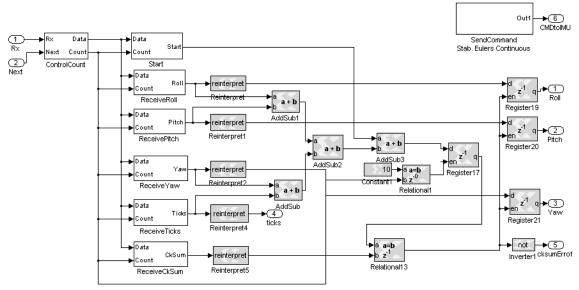

| Figure 62: | IMU Control Count Subsystem                           | . 97 |

| Figure 63: | IMU Send Command Subsystem                            | . 98 |

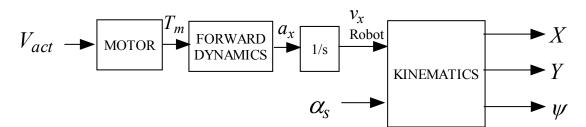

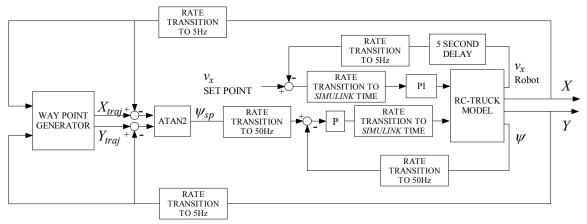

| Figure 64: | RC-Truck Model Block Diagram                          | . 99 |

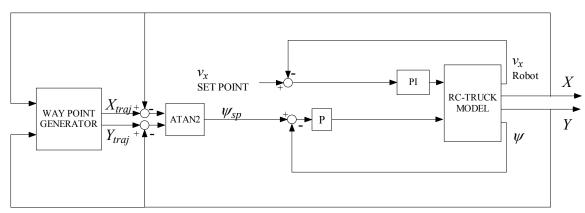

| Figure 65: | RC-Truck Control System                               | 100  |

| Figure 66: | Modified RC-Truck Control System               | 101 |

|------------|------------------------------------------------|-----|

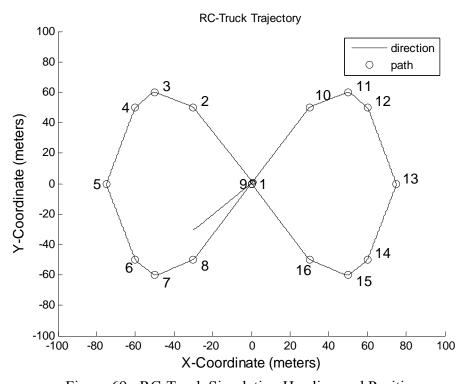

| Figure 67: | Simulink Implementation of Way Point Generator | 102 |

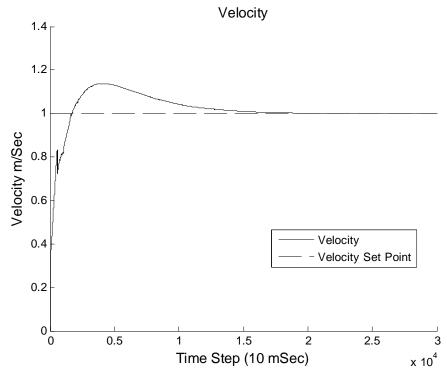

| Figure 68: | RC-Truck Simulation Velocity Output            | 103 |

| Figure 69: | RC-Truck Simulation Heading and Position.      | 103 |

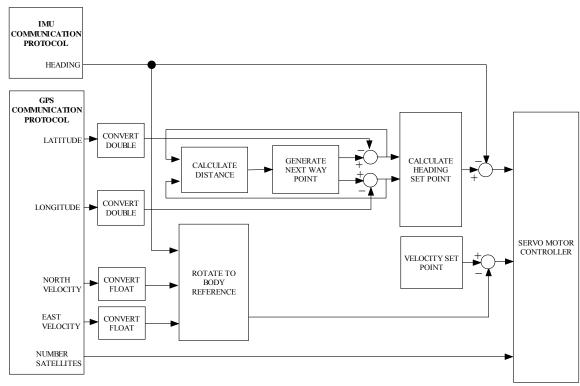

| Figure 70: | Hardware RC-Truck Control System               | 105 |

| Figure 71: | RC-Truck with Sensors and Power Supply         | 107 |

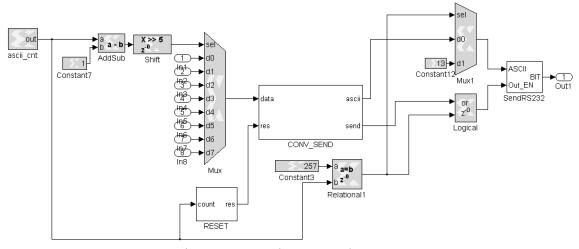

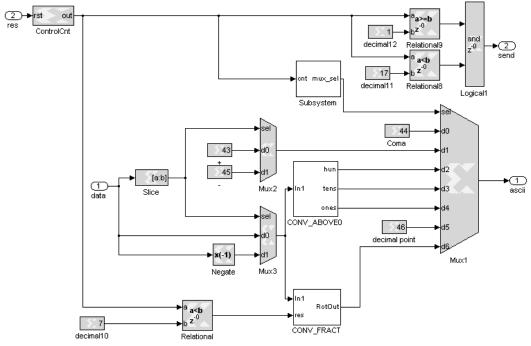

| Figure 72: | Send ASCII Subsystem                           | 108 |

| Figure 73: | Convert to ASCII Subsystem                     | 110 |

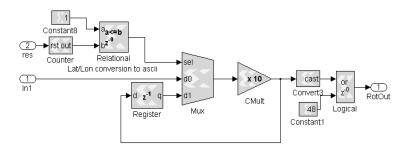

| Figure 74: | Convert Fraction to ASCII                      | 111 |

| Figure 75: | FPAA Program for Battery Monitoring            | 112 |

| Figure 76: | Program for Battery Monitoring                 | 113 |

| Figure 77: | Single and Double Representation Word Format   | 114 |

| Figure 78: | Double to Binary Conversion                    | 116 |

| Figure 79: | Heading Set Point Control Subsystem            | 117 |

| Figure 80: | Hardware Way Point Generator M-File            | 118 |

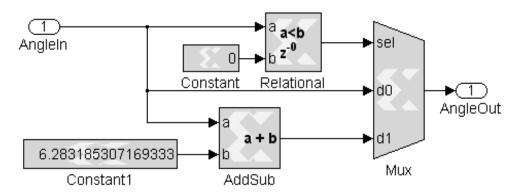

| Figure 81: | Heading Correction Subsystem                   | 120 |

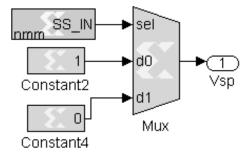

| Figure 82: | Velocity Set Point Subsystem                   | 121 |

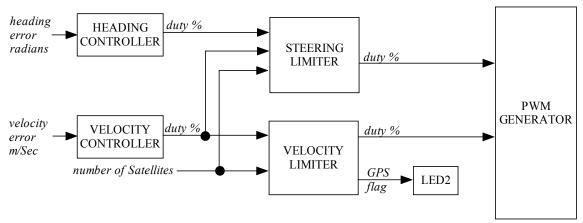

| Figure 83: | Servo Control Block Diagram                    | 122 |

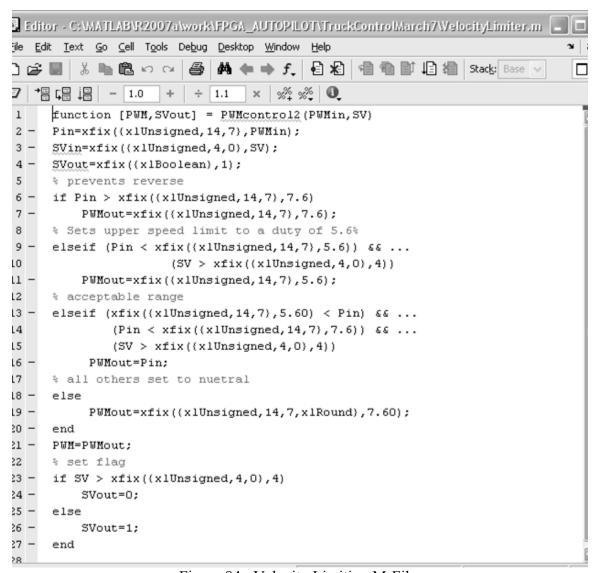

| Figure 84: | Velocity Limiting M-File                       | 124 |

| Figure 85: | Steering Limiting M-File.                      | 125 |

| Figure 86: | Velocity Response for Trial One                | 126 |

| Figure 87: | Trajectory for Trial One                       | 127 |

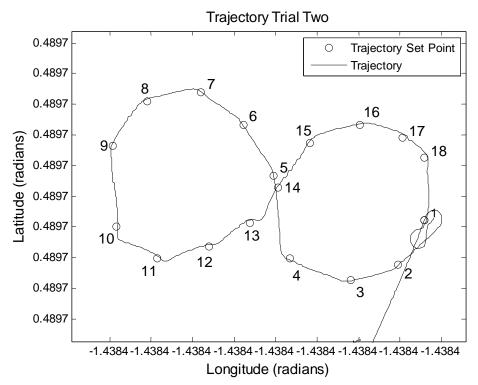

| Figure 88. | Velocity Response for Trial Two                | 127 |

| Figure 89: Trajectory for Trial Two                              | 128 |

|------------------------------------------------------------------|-----|

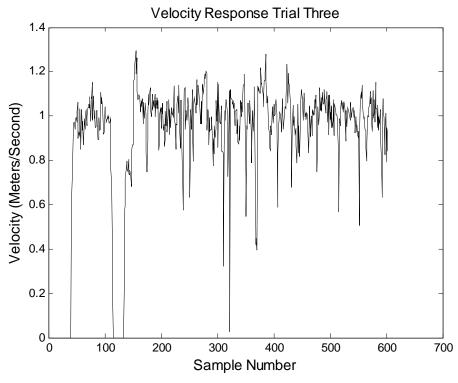

| Figure 90: Velocity Response for Trial Three                     | 128 |

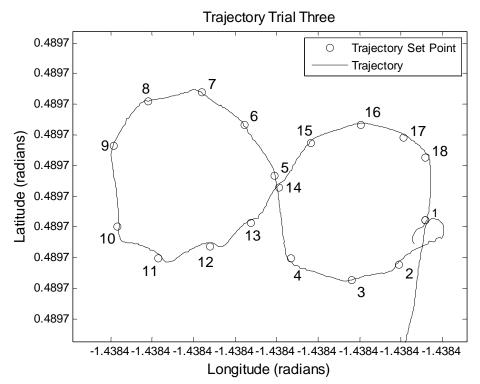

| Figure 91: Trajectory for Trial Three                            | 129 |

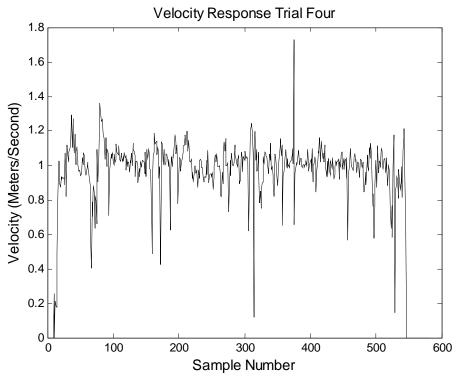

| Figure 92: Velocity Response for Trial Four                      | 129 |

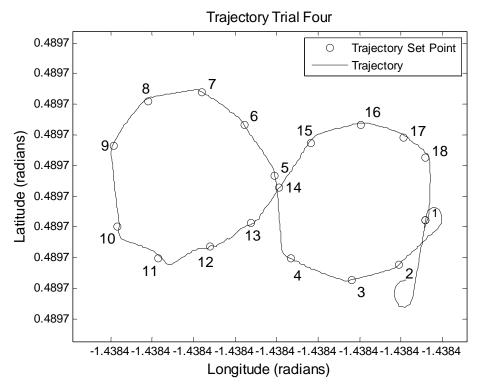

| Figure 93: Trajectory for Trial Four                             | 130 |

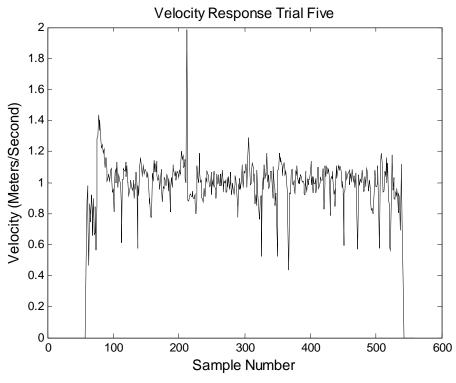

| Figure 94: Velocity Response for Trial Five                      | 130 |

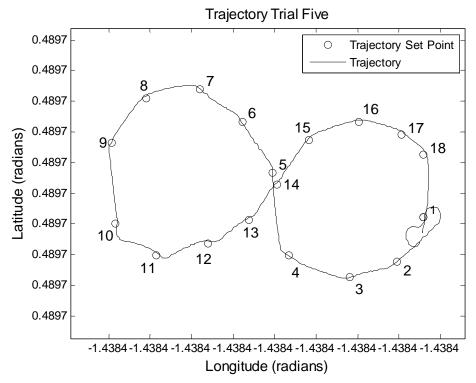

| Figure 95: Trajectory for Trial Five                             | 131 |

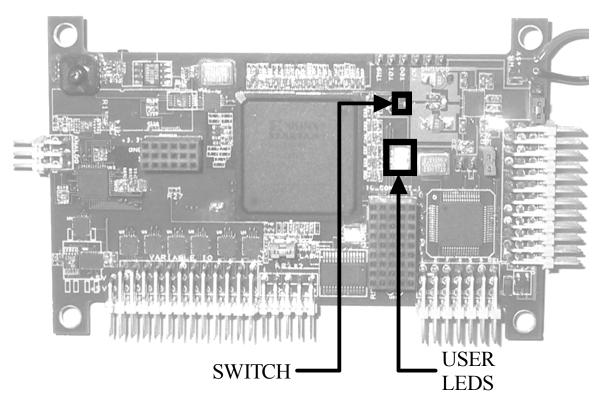

| Figure 96: User LEDs and Switch Locations                        | 144 |

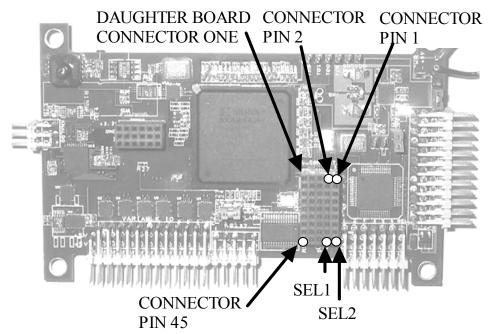

| Figure 97: Daughter Board Connector One                          | 145 |

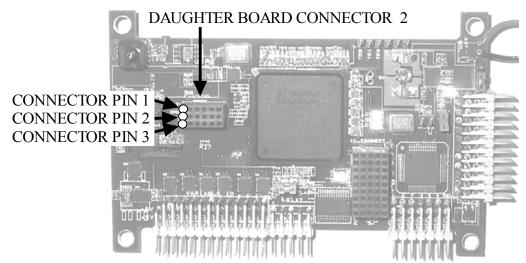

| Figure 98: Daughter Board Connector Two                          | 147 |

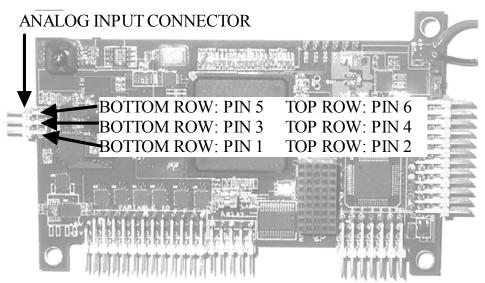

| Figure 99: Analog Input Connectors.                              | 148 |

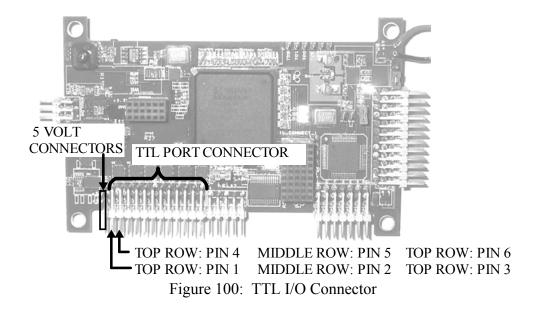

| Figure 100: TTL I/O Connector                                    | 149 |

| Figure 101: PWM Port Connections                                 | 151 |

| Figure 102: PWM Pilot Input Connector                            | 153 |

| Figure 103: RS232 Connector                                      | 154 |

| Figure 104: Flash Memory Circuit                                 | 155 |

| Figure 105: Variable I/O Port Potentiometer Circuit              | 155 |

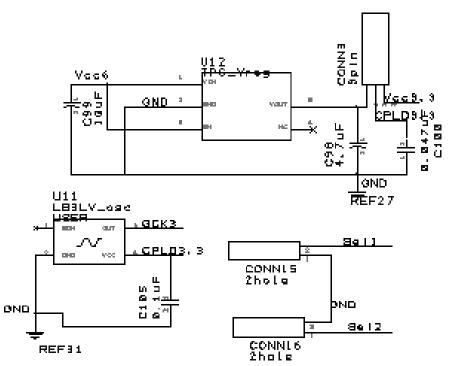

| Figure 106: Variable I/O Port Translator and Connector Circuitry | 156 |

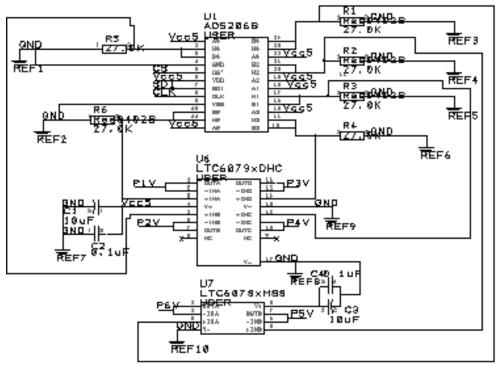

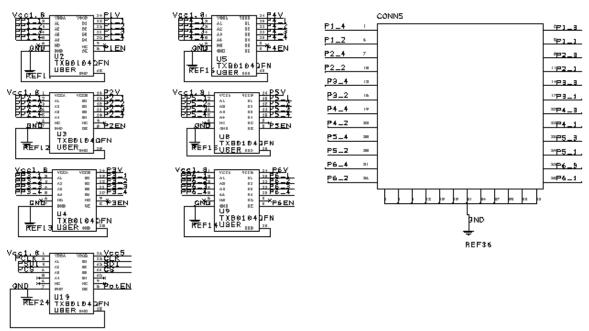

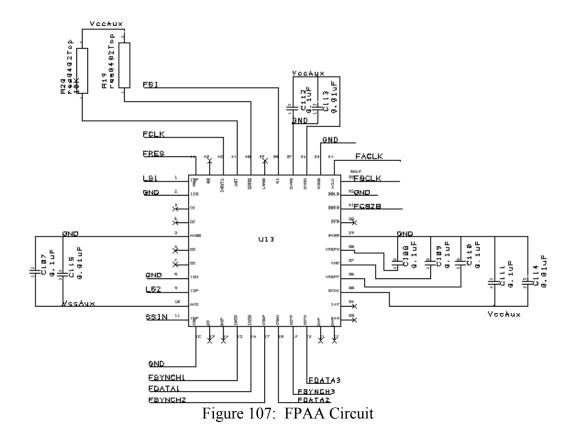

| Figure 107: FPAA Circuit                                         | 156 |

| Figure 108: FPAA Input Circuit                                   | 157 |

| Figure 109: Safety Switch Power and Clock Circuit                | 157 |

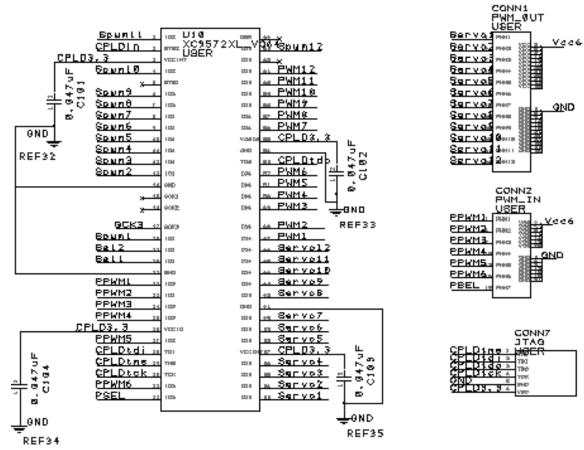

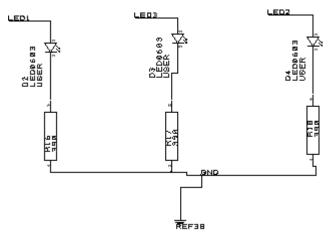

| Figure 110: Safety Switch CPLD and Connector Circuit             | 158 |

| Figure 111: User LED Circuitry                                   | 158 |

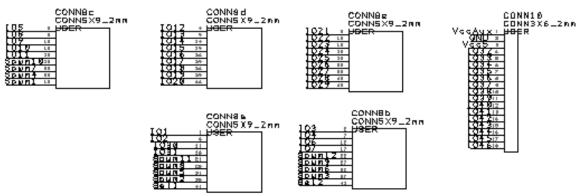

| Figure 112: | Daughter Board Connection Circuit | 159 |

|-------------|-----------------------------------|-----|

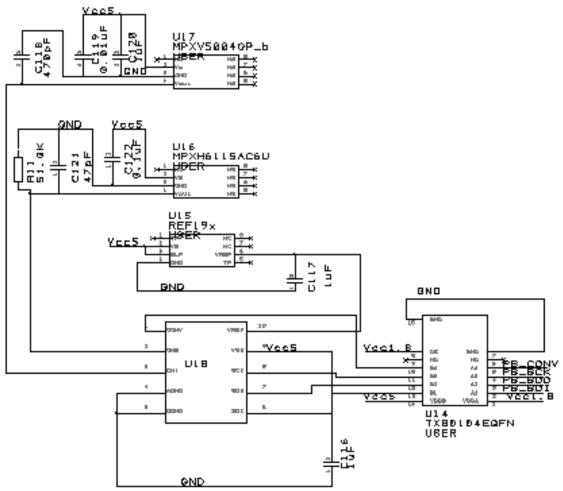

| Figure 113: | Pressure Sensor Circuitry         | 159 |

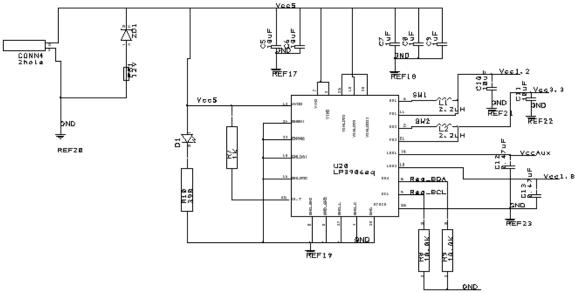

| Figure 114: | Power Supply Circuitry            | 160 |

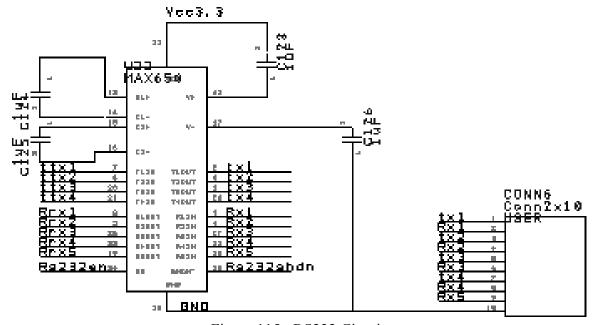

| Figure 115: | RS232 Circuit                     | 160 |

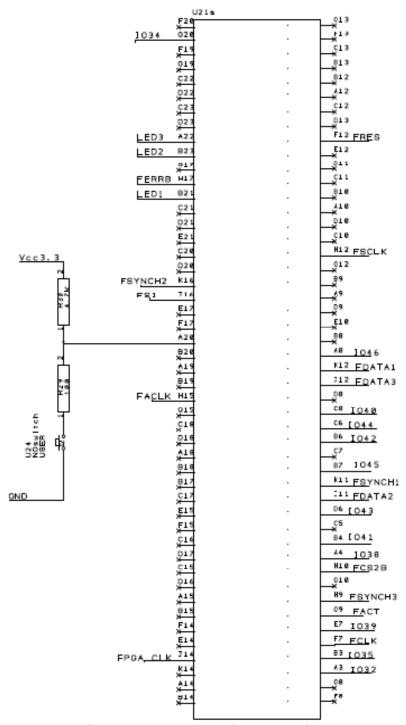

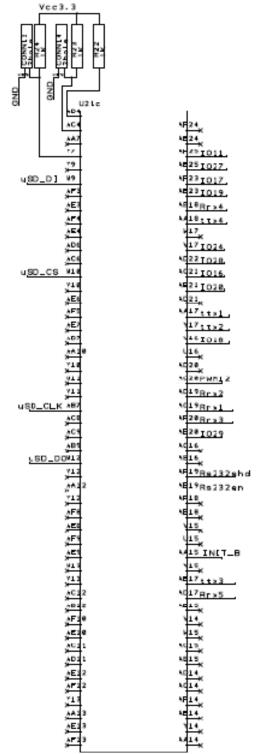

| Figure 116: | FPGA Bank0 Connections            | 161 |

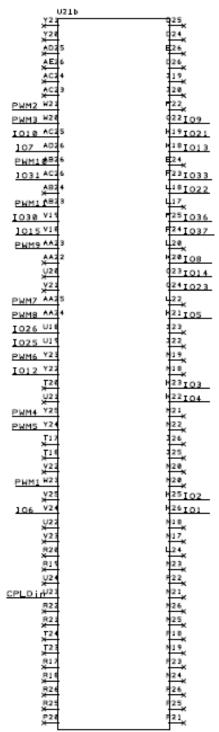

| Figure 117: | FPGA Bank1 Connections            | 162 |

| Figure 118: | FPGA Bank2 Connections            | 163 |

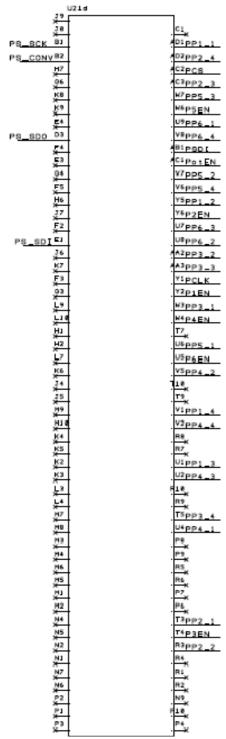

| Figure 119: | FPGA Bank3 Connections            | 164 |

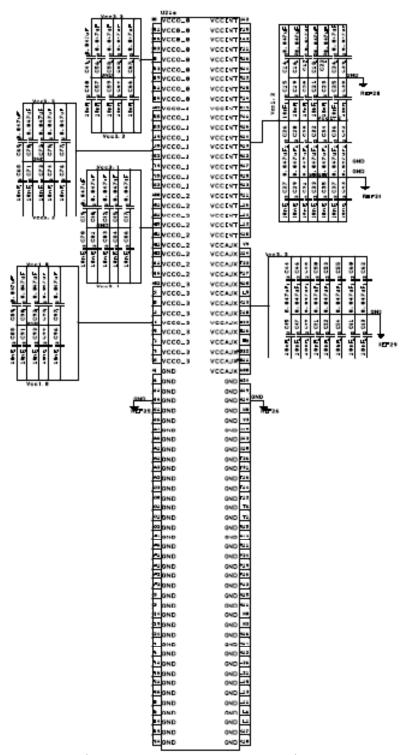

| Figure 120: | FPGA VCC Connections              | 165 |

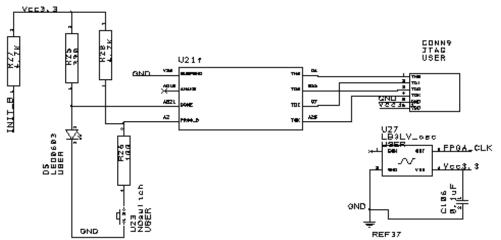

| Figure 121  | FPGA JTAG and Clock Circuit       | 166 |

# DEVELOPMENT OF AN FPGA BASED HARDWARE PLATFORM FOR RESEARCH AND DEVELOPMENT OF AUTONOMOUS SYSTEMS WENDY ALVIS

#### **ABSTRACT**

Unmanned vehicles, both ground and aerial, have become prevalent in recent years. The research community has different needs than the industrial community when designing a finalized unmanned system since the vehicle, the sensors and the control design are dynamic and change frequently as new ideas are developed and implemented.

Current autopilot hardware, which is available as on-the-market products and proposed in research, is sufficient for unmanned systems design. However, this equipment falls short of being able to accommodate the needs of those in the research community who must be able to quickly implement new ideas on a flexible platform.

The contribution of this research is the realization of a hardware platform, which provides for rapid implementation of newly developed theory. Rapid implementation is gained by providing for software development from within the *Simulink* environment and utilizing previously unrealized flexibility in sensor selection. In addition to the development of the hardware platform, research was performed within *Simulink*'s System Generator environment in order to complement the hardware. The software produced consists of a user template that integrates to the selected hardware. The template creates a user friendly environment, which provides the end user the capability to develop

software algorithms from within the *Simulink* environment. This capability facilitates the final step of full hardware implementation.

The major novelty of the research was the overall FPGA based autopilot design. The approach provided flexibility, functionality and generality. The approach is also suitable for and applicable to the design of multiple platforms. This research yielded a first time approach to the development of an unmanned systems autopilot platform by utilizing:

- Development of programmable voltage level digital Input/Output (I/O), ports,

- Utilization of Field Programmable Analog Arrays (FPAA),

- Hardware capabilities to allow for integration with full computer systems,

- A full Field Programmable Gate Array (FPGA), implementation,

- Full integration of the hardware within *Simulink*'s System Generator Toolbox.

#### **CHAPTER 1**

### **INTRODUCTION**

Unmanned vehicles are better for the performance of tasks that are considered "dull", "dirty" and "dangerous" than piloted crafts. There are many potential uses that will provide a benefit to society such as traffic monitoring, search and rescue and monitoring of structures such as dams and bridges. The use of Unmanned Aerial Vehicles (UAVs), in the military dates back to the 1940s when they were used to fly into radioactive clouds to collect samples. As technology progressed Unmanned Aerial Vehicles have evolved into smaller and more efficient aircraft. UAVs have increasingly demonstrated their benefit to the military. Pioneer has flown reconnaissance missions in the Persian Gulf, Kosovo, and Bosnia since the early nineties. More recently additional types of crafts have been developed and have continued to fly these types of missions to the present, [1].

There is a great deal of work taking place in the research community to make improvements in the existing technologies. The wide diversity in unmanned vehicle designs and control as well as diversity in existing autopilots has lead to major compatibility issues among different platforms. The compatibility issues introduce an additional challenge to the research community. The platforms, sensors and control algorithms are dynamic and change frequently as new ideas are developed and implemented.

A search was completed for pre-developed hardware that would allow for data acquisition for system identification, testing/implementation of controller design and flexibility of platform and sensor selection. It was apparent that what is currently available requires a considerable knowledge of programming digital processing hardware and embedded control design. In addition, the hardware available only provides for a very limited choice of sensor selection with each of the specific autopilots.

Within the research community, there are two prevalent forms of processing platforms. Digital Signal Processor, (DSP), systems exist such as Mini-ITX and full computing systems such as PC-104. Neither of these implementations fully meets the needs of the unmanned system researcher. The DSP implementation requires knowledge of embedded systems design and lacks parallel processing capabilities. The full computing system requires knowledge in programming real time operating systems in order to meet tight timing requirements. Some research has been performed, which considered the inclusion of Field Programmable Gate Arrays, (FPGAs), for additional flexibility and parallel processing capabilities. Thus far none have included integration with software providing a higher level of abstraction than Very-high-speed integrated circuit Hardware Description Language, (VHDL). In addition, the advantages of hardware-in-the-loop capabilities for design verification have been explored only minimally.

The DSP and FPGA implementations have the benefit of allowing for precise real time control. This is a mandatory requirement with autopilot systems and is very carefully met with this research. However, in order to take advantage of the flexibility

and the parallel processing capabilities that are not available with DSP processors this precise timing was realized with a FPGA.

The lack of availability of autopilots meeting the research community requirements was the motivation behind this research. The outcome was a hardware platform, which provides two major capabilities. The platform provides for a commercial off-the-shelf, (COT), language to be utilized for both programming and hardware-in-the-loop simulation. In addition, the platform provides sufficient flexibility to allow a wide variety of sensors to be available for use with the system under study.

When proposing a new autopilot platform, issues such as sensor integration, sensor diagnostics, conventional servo and actuator control, as well as switching among, or modifying control techniques if and when necessary must be taken into consideration. In other words, consideration should be given to implementing different controllers and sensor selection based on different mission profiles and selected robotic platforms. Thus, any proposed design must include an interface module that provides for simulation, validation and verification before actual implementation. By default, such a design should be fully interfaced and integrated with MATLAB/Simulink, which provides for a higher level of abstraction for programming and hardware-in-the-loop capabilities.

Considering vehicle payload limitations, power consumption and requirements, cost-effectiveness and available 'space' on the unmanned vehicle are primary. Given the fact that real-time control requires very strict and fixed timing for stability purposes, the embedded system approach is preferred in designing an autopilot. This approach can be implemented in a much lighter package, which makes it suitable even for miniature vehicles.

Swarm formation and mission planning algorithms have been successfully designed on standard computing systems such as the Mini-ITX or PC-104. However, without an additional autopilot, the programmer must have an extensive knowledge of real-time operating system programming to ensure the signal processing and control system meets the timing requirements of the vehicle dynamics. The hardware capability for full integration with these previously developed systems was designed into the autopilot. When in use with these systems the autopilot can be programmed to become the "slave" to the "master" computer and follow specified trajectory commands. This capability provides researchers familiar with software implementations such as C-programming running on Linux to continue with their work unimpeded by the difficulty of implementing real-time programming.

The final area of concern is the protection of the hardware and any surrounding objects or humans. Hardware failure can have catastrophic effects, especially when such failures are associated with aerial vehicles. A loss of control with an unmanned helicopter can very easily cause serious injury or even loss of life. Many systems already allow for emergency takeover by a human pilot. However, this design can be taken even further when used with an external computing system. Providing the end user the ability to design fault detection and emergency control algorithms from within an external computer provides the system with another form of redundancy. In order to achieve this form of redundancy an additional safety switch circuit was designed into the autopilot platform. The safety switch circuit provides for emergency takeover by either a human pilot or a secondary daughter board. The secondary daughter board can be designed to

communicate with a computer and take control of the actuators under autopilot failure conditions.

The developed autopilot hardware platform complements the full computing systems by providing a separate processing system that handles the sensor signals and actuator outputs. In addition, it has the ability to be used as a standalone platform for very small scale vehicles. Some systems have been designed with flexibility and ease of implementation in mind. However, this research resulted in an improvement over what has been previously proposed or developed by allowing for full integration with *Simulink*. The integration with *Simulink* provides for a higher level of programming abstraction, hardware-in-the-loop capabilities and full FPGA implementation. These capabilities maximize parallel processing capabilities, analog signal conditioning, which can be predefined and initiated through digital communications from the FPGA processor. In addition, they provide an additional layer of safety by providing for control of the actuators by either a pilot utilizing a handheld radio or a daughter board.

The contribution of this research is a flexible, hardware-in-the-loop capable platform that benefits the area of unmanned systems design by providing for the rapid prototyping of new theory. Therefore, a reduction in the time it takes the benefits to become applicable is realized in both the private and military sectors. The improvements over previous work have resulted from the novelty of utilizing a full Field Programmable Gate Array, (FPGA), implementation, which provides full integration with *Simulink*'s System Generator Toolbox. Surrounding analog circuitry was developed to provide a more flexible interface than realized by previous work. The flexible interface was realized through the development of programmable digital ports along with utilization of

Field Programmable Analog Arrays for different analog inputs. In addition, software was produced to provide for a *Simulink* template, which integrates with the autopilot hardware. The software provides a user friendly environment, which provides the end user to more easily integrate the completed algorithms with the sensor and actuator hardware.

The developed autopilot platform was tested utilizing an RC-Truck like robot. Existing software for simple way point following of a robot built for a Traxxis RC-Truck was implemented on the autopilot. The autopilot was integrated to the servo controllers of a MicroStrain IMU and a Superstar II GPS unit. The RC-Truck was able to successfully follow way points, which demonstrated the effectiveness of the hardware design.

#### **CHAPTER 2**

#### RELATED WORK

There exist several UAV/VTOL autopilot hardware platforms, which are sold as fully developed systems. These systems have worked well for those in the private sector. However, the research community has still felt the necessity to develop their own processing systems. Some were developed as a portion of the overall research and others were the subject of the research itself. Each of the, on-the-market, autopilots will be discussed in the context of flexibility, methods of programming, hardware-in-the-loop capabilities and inclusion of parallel processing capabilities. The research based processing systems will be discussed as a generality of the different hardware types in Section 1.1. A more detailed discussion will be presented of the hardware platforms developed specifically as the subject of the research in Section 2.2. An overview and comparison of the types of platforms is presented in Section 2.3.

# 2.1 Commercial Autopilots

There are several autopilots on the market. Most of these autopilots have not taken into consideration all of the needs of the research community. These autopilots can be separated into several categories. Autopilots, which are proprietary and lack user design capabilities. Autopilots, which are very basic in processing power and possess limited capabilities. Autopilots, which do have flexibility in reprogramming but do not have all the capabilities of the design presented in this dissertation.

Two autopilots, which were designed for use with specific vehicles sold by the company marketing the entire system, are available. The Generation II by BAI only provides for minor modification, [2, 3]. The Rotomotion device provides for no modifications at all, [4]. Only minor details are provided about these designs due to the proprietary nature of the entire system. Neither is suitable as a platform for research due to the built in dependency on the company for airframe specific modifications to the software.

The Kestral by Procerus, [5], and the MP2028 by Micropilot, [3, 6], include user flexibility designed into the system. Unfortunately, both of these devices are still proprietary in nature. There are additional input/output ports included in the system software sold for reprogramming and hardware-in-the-loop capabilities. However, both designs only provide reprogramming and hardware-in-the-loop capabilities through proprietary software, which prevents use with *Simulink* and limits flexibility. Details on the Kestral are given in Table 7 and the MP2028 details are given in Table 8. Both tables are presented in Appendix A.

The Ezi-Nav, by Autonomous Unmanned Air Vehicles, was designed to be a low cost autopilot with minimal capabilities, [3, 7]. It contains eight separate microprocessors that share the computational load. The Ezi-Nav operates solely with handheld GPS units and possesses no additional ports for communications with an external processor or additional sensors. More details for Ez-Nav are provided in Table 9, Appendix A. While the Ezi-Nav has demonstrated successful flights with fixed wing vehicles, it does not have the flexibility or processing capabilities required by the research community.

The Phoenix, by O-Navi, is an open source, fully reprogrammable autopilot, which utilizes a 32MHz, 32-bit Motorola processor, [8, 9]. Phoenix is programmable through a provided flash kit. However, it still lacks the ability to interact with *Simulink* and there is no hardware-in-the-loop capabilities provided for in the design. Details are presented in Table 10, Appendix A.

The Piccolo II, by Cloudcap, is an open source autopilot designed specifically for fixed wing vehicles, [3, 10]. Piccolo II possesses sufficient flexibility that implementation with rotary wing vehicles appears reasonable. Piccolo II is popular with the research community. The popularity is, most likely, due to its flexibility and ability to be programmed through *Simulink*'s Real Time Workshop. In addition, it does allow for hardware-in-the-loop implementation with *Simulink* models. However, the computer running *Simulink* must be equipped with a CAN interface card. Piccolo II comes close to meeting the research community's requirements. However, it lacks the parallel processing capabilities and flexibility of a full FPGA design. Details of the Piccolo II are given in Table 11, Appendix A.

Of all the autopilots on the market, the Microbot, by Microbotics, possesses the most flexibility designed into the system, [11]. It is the only open source design on the market that includes an FPGA to provide for reconfiguration of up to 32 I/O ports. In addition, an expansion board provides for two asynchronous serial ports and twelve analog inputs to be included in the design. Unfortunately, the FPGA is only utilized for the input and output logic. Most of the autopilot's programming resides in a single microprocessor, which does not allow any parallel processing of the main functions. Another major disadvantage of Microbot is its lack of a design capability for rapid

prototyping. While the unit is fully reprogrammable, it does not provide for programming through *Simulink*. Additionally, Microbot does not possess any hardware-in-the-loop capabilities designed into the system. More details are provided in Table 12, Appendix A.

All of the autopilots, except the Microbot, are limited by a lack of parallel processing, which is afforded by a FPGA implementation. In addition, none provide analog input flexibility or have hardware-in-the-loop capabilities with *Simulink* specifically incorporated into the design. The Microbot design, with the FPGA being utilized for sensor sampling and data/servo output, does remove some of the computational load from the microprocessor. The Microbot design also provides considerable flexibility across platforms and sensors. While this design is superior to the others with respect to flexibility, it falls short in simple programming and hardware-in-the-loop capabilities.

#### 2.2 Related State of the Art Research

The majority of publications studied discussed the processing system as a brief portion of a larger research project. In these papers two popular methods dominated. One involved implementing a low power DSP/microprocessor chip such as a Mini-ITX board. The other involved implementing a full motherboard type system such as the PC-104 system. The microprocessor and low power DSP chip possess minimal processing power. Both chips are used primarily for either one specific system, which does not require complex calculations, or a micro-air vehicle that has minimal payload capacity. Only the most recent publications have begun to consider the advantages of a FPGA's parallel processing and reconfigurable capabilities. Section 2.2.1 will discuss low power

processor implementations. Section 2.2.2 will discuss the full motherboard implementations. Section 2.2.3 will cover what has been accomplished or has been proposed for full FPGA and hybrid FPGA/DSP implementations.

# 2.2.1 Microprocessor/DSP Low Power Autopilots

Jung et. al., designed a simplified autopilot for use with a specific fixed wing aircraft, the Goldberg Decathlon ARF, [12]. The design was performed as a learning lab tool for undergraduate students at Georgia Tech. A Rabbit 3000 microprocessor was used along with several sensors. This microprocessor meets the requirements for easy implementation of simple algorithms, which are used for teaching basic control theory. However, the Rabbit 3000 does not provide flexibility for use across platforms. A similar design was developed by Brigham Young University with a fixed wing aircraft fabricated in foam, [13]. As with the system developed by Georgia Tech, the autopilot was small, easy to implement and did function properly. However, the autopilot suffered from inflexibility across platforms. In addition, neither designs provided hardware-in-the-loop capabilities.

Kahn and Kellogg designed an autopilot system that utilized Microchip's 16F877 microcontroller for a kite style micro-air vehicle, [14]. Since the system possessed low dynamics and utilized a minimal amount of sensors, very little processing power was required. Microchips line of microcontrollers is low cost and easy to program. However, they possess a maximum clock frequency of 20MHz, a buffer for serial communication that is limited to three characters and no hardware-in-the-loop capabilities. Microchips line of products does not meet the requirements specified for the majority of unmanned systems research.

Preliminary designs are presented for an MC68HCS12 microcontroller based design, [15]. The design focuses on providing a low cost and easy to modify system. The specific UAV and sensors are not mentioned. However, the processing power and flexibility across platforms will be limited due to the selection of a microcontroller for processing as opposed to an FPGA. In addition, there is no mention of intentions to design, into the system, any hardware-in-the-loop capabilities.

An area of research gaining popularity is the design of micro-air vehicles. The payload capacity for these systems is quite small, which limits the size and power consumption of the selected computing system. The majority of researchers in this field are implementing the algorithms with microcontrollers. The microcontrollers chosen are primarily from Microchip's line of processors, [16-18]. Several publications were studied, which discussed either custom sensor design or vehicle design. However, none had implemented any onboard processing. Other methods were used for control of the vehicle. A ground station was used for control processing, [19]. A ground station was also used for verification of design by simulation, [20-25]. Handheld radio control was investigated, [26, 27]. A tethered system was connected to a DSP board and MATLAB, [28]. As new vehicle and sensor designs are developed and become ready for implementation, a processing platform is required. This requirement further demonstrates the need for a small research oriented autopilot platform.

# 2.2.2 Full Computer Implementations

The majority of research publications discussing the design of small scale unmanned systems present full motherboard systems without dedicated hardware for the signal processing algorithms and low level controllers. The most popular is the PC-104

board running a real-time operating system such as VxWorks® [29] or QNX [30-32]. Lee, et. al., incorporated a full data acquisition card in the design, [32]. Various other computing systems have been used with real-time operating systems as well, [33, 34].

All of these implementations follow the same basic design principle, external sensors and hardware with a single standard computing system. This method has been proven to work successfully. However, great care must be taken in programming the control system or the precise timing needed for the control of the vehicle dynamics will not be met. This requires a great deal of knowledge in control systems and in the real-time programming language. Each function must be given a priority, which allows those functions with the lowest priorities to be permitted to run only when the highest priorities have completed. For a final implementation, which is designed only once, this method may prove acceptable. However, whenever the control system is modified significantly the entire low level control program changes and the timing issues must be entirely reconsidered. For example, if PID controllers are replaced by H-infinity feedback controllers all timing issues would have to be revisited. This potential software redesign can create longer delays between deriving new theory and implanting it in hardware.

One design did try to solve some of these issues by implementing a two processor system running on RT-Linux, [35]. The software was designed with a layered approach. A main board ran an x86 compatible motherboard for the wireless GPS communications and mission planning. The ATM Mega 163 chip was utilized for real-time flight control processes. This is the same basic concept of using a dedicated autopilot for the low level control system, which further argues the need for the hardware platform presented.

# 2.2.3 Implementations Utilizing FPGAs

FPGAs are very slowly gaining popularity due to the recent advances in increased number of gates and simplification of design by the manufacturer's providing intellectual properties, IPs. The IPs provide pre-developed functions such as complicated mathematical calculations and RAM, which would normally be time consuming to develop utilizing a HDL. Since these advances are fairly recent, there are only a few publications following the same philosophy of utilization of FPGAs, [9, 36-40].

Klenke combined a 40K FPGA with an 8-bit microprocessor for control of a fixed wing aircraft with a GPS unit as the only sensor, [39]. The FPGA array was utilized for the FM aircraft receiver and the servo control. The system worked successfully and proved to be a simple to implement, inexpensive design. However, it does not possess the processing power or flexibility required for research across platforms and sensors.

A proposed FPGA based design to provide a system capable of integrating a propulsion health system with a control system for VTOLs has been presented, [36]. This design recognized the strength of both a FPGA architecture and integration with *Simulink* for programming. However, the proposed design intends to implement the algorithms running inside the FPGA under a real-time operating system, VxWorks®. In order to provide user programmability, the intention is to create an ICD along with third party software for programming. The system will implement a Vibe Card for receiving some sensor data. With some simple front end analog signal conditioning and A/D converters, this card can be eliminated and all of the signal processing can be implemented entirely on the FPGA chip. In addition, the design also includes a Geode

DSP processor, which will run a majority of the processes. This aspect of the design ultimately limits the system to sequential processing for the majority of the processes.

A flexible FPGA/DSP based autopilot has been developed by the Georgia Institute of Technology, [37, 38]. The project has been completed and tested on two separate platforms. One system works in conjunction with a "master" computing system on the GTMax. Another system acts as a stand-alone device on the GTSpy. While a flexible hardware-proven design is defined, the full strength of the Xilinx line is not utilized to full advantage. The majority of the processing on-board the Xilinx chip is performed by a soft core DSP running on the MicroC/OS II real-time operating system. As a result of the sequential nature of the operating system, many of the tasks cannot be divided into smaller tasks running in parallel. In addition, the system includes a separate DSP chip to run any high level processing. This configuration prevents the system from being fully integrated with *Simulink* through the use of the System Generator toolbox.

Virginia Commonwealth University has recently demonstrated a successful in flight test of a FPGA based autopilot. [9]. This autopilot utilized a Suzuku V board containing a Xilinx II FPGA chip, 32 M Bytes of SDRAM, 8 M Bytes of flash memory and an Ethernet interface. The FPGA's on-chip PowerPC runs a Linux kernel for implementation of the majority of the processing. The goal of the research was to demonstrate that the software could be developed in commercial off-the-shelf hardware and then ported to any other hardware running the same Linux kernel. Since the focus of the research was not a complete hardware autopilot design, the ability to run processes in parallel, with the exception of the I/O protocol, was not considered. In addition, it did not take advantage of the Virtex II Simulink capabilities for programming and hardware-in-

the-loop verification. However, the design does demonstrate the capabilities of the FPGA as the processing hardware for an autopilot.

Continuing work on the design of an FPGA based control system for a Micro-Satellite has demonstrated the potential benefits of FPGAs for autopilots, [40]. The Xilinx series of FPGAs is utilized and full parallel processing utilized. While in-flight tests have not yet been demonstrated, lab tests have indicated that good timing and parallel communication with the devices have been obtained.

# 2.3 Overview of Autopilot Implementations

While standard computing systems have been proven to work successfully, great care must be taken in programming the control system or the real-time requirements will not be met. Whenever the control system is entirely changed, which occurs frequently in research, the entire low level control program changes and the timing issue must be entirely reconsidered. This leads to a longer design time between deriving new theory and implanting it in hardware. A solution to this problem is to include a separate processor. Such an autopilot is presented in this dissertation. The autopilot provides an off-board system that follows a given trajectory while handling the tight timing constraints required for sensor integration and control of the vehicle dynamics.

The majority of the systems presented implement a single processor. The processing power varies depending on the specific chip selected. The single processer design is at a disadvantage when compared to implementing either a full FPGA or a hybrid DSP/FPGA design. Since single processor systems cannot operate with parallel processing, care must be taken to be sure that each of the asynchronous sensor inputs are sampled at the correct time while also updating the servo outputs. In addition, the

majority of the implementations do not allow for *Simulink* integration or hardware-in-the-loop verification of the design.

Several of the FPGA implementations have benefited from the flexibility and parallel processing capabilities of the FPGA with regard to managing I/O functions. These designs failed to carry the parallel processing capabilities into the majority of the processes by implementing most of the algorithms within an on-board or external DSP. The only work that has utilized the full parallel capabilities for flight control was for the design of a Micro-Satellite. This work did indicate good timing when utilizing the parallel capabilities of the FPGA implementation. However, it did not explicitly design *Simulink* integration into the system.

This research included the benefit of *Simulink* integration, as with [10], the flexibility of inputs resulting from utilizing an FPGA, as with [9, 11, 36, 37], and produced a significant contribution to the field of unmanned systems by including further capabilities. These capabilities include full FPGA implementation, full integration with *Simulink* for both programming and hardware-in-the-loop, programmable signal conditioning and hardware so the human pilot can easily regain control under failure conditions. An additional layer of safety was also included. When in operation with a daughter board and second processing system, the secondary system is able to take over control of the aircraft servos when a failure in the autopilot has been detected.

#### **CHAPTER 3**

# **AUTOPILOT REQUIREMENTS**

There are two primary areas of study, which will utilize the autopilot differently. Specifications for high level mission planning and vision systems differ considerably from those for system level applications. System level research includes the development of control systems for vehicle dynamics, development of methods for filtering and integrating the sensors and development of new micro-air vehicles.

Navigation researchers work directly with the sensor inputs in order to generate minimal noise and maximum accuracy of certain variables such as position, velocity and acceleration. Researchers within the area of controller design are investigating the most promising methods of controlling the dynamics of the vehicle. Both groups require certain measurements to be available and accurate. The researcher developing the control algorithms will require that the underlying autopilot platform provide for completed sensor filtering and integration. This provision ensures that signals have clearly defined variables and can be utilized within the control loop without modification to filtering and integration modules.

Researchers investigating micro-air vehicles are concerned with the development of new platforms requiring custom controller design. In addition, they are very concerned with the development of new smaller size and low power sensors. This group will have the same requirements as the control and navigation researchers. Additionally,

they are confronted with requirements of providing for various sensor inputs, which cannot be predetermined, as well as low power and light weight circuitry demands.

Since both the navigation and control researchers will be implementing and testing algorithms, many of the requirements, which simplify the process, pertain to both groups. These capabilities include modularity for separation of algorithms, a high level of abstraction to allow for simplification of design and the ability for hardware-in-the-loop verification of the software algorithms. The majority of researchers working in this area utilize <code>Simulink/MATLAB</code> for testing algorithms. Therefore, the ability to program directly from <code>Simulink</code> is advantageous. <code>Simulink</code> software design is also well suited for high levels of abstraction and the type of modularity required between the navigation system and the vehicle control system. In addition, providing for hardware-in-the-loop simulation directly with <code>Simulink</code> models is beneficial for testing designs without the risk of loss of hardware. For these reasons, full integration with <code>Simulink</code> is an extremely valuable aspect of the autopilot platform developed during this research.

The researchers working with navigation systems and vehicle design will require that data be collected for system identification of the sensors or the dynamics of the vehicle. This requires that a significant amount of data be stored while the vehicle is in flight. In addition, the hardware must have the capability to store this information at a high sampling rate without interrupting the modules controlling the navigation. This requirement clearly argues for parallel processing capabilities and creates a further requirement of additional memory for data collection.

When working with high level mission planning or vision research, it is necessary to be able to send the way points to the navigation modules and have the vehicle follow

the trajectories without consideration for designing around tight timing constraints. In addition, many of the researchers in this area of research prefer to work with systems such as the Mini-ITX DSP processor or the PC-104 type microprocessor. In order to meet the needs of this area of research, interaction with this second processing system must be included in the design. The autopilot must have the ability to send and receive commands through serial RS232 communication. The software controlling the dynamics of the vehicle, which provides for trajectory following, is a platform-specific design. The autopilot platform must provide for rapid development so that once the vehicle is selected, the navigation and dynamic control system can be quickly finalized. This capability provides for timely and efficient development of applications such as vision, swarm formation and mission planning while running on a complete computing system.

When working with aerial vehicles, safety requirements must be given the highest of priorities. Safety requirements demand as much redundancy for actuator control as possible. The autopilot produced during this research was developed to work with an external processor. Therefore, a redundancy of control hardware was already present. However, additional hardware was incorporated to provide for transfer of actuator control to either a human interface or a second processing system.

The list of generalized requirements, which were incorporated in the platform developed during this research includes:

Integration with MATLAB/Simulink for a higher level of abstraction and modularity when programming and the capability for hardware-in-the-loop verification,

- Adequate memory for data collection for use with system identification research,

- Analog design to allow for reconfigurable cross platform/sensor capabilities,

- RS232 communications to provide for integration with a second computing system,

- Parallel processing capabilities & hardware level timing control,

- Emergency takeover of servos as an additional layer of safety.

## **CHAPTER 4**

#### **AUTOPILOT ENVIRONMENT**

When designing the autopilot, careful consideration was given to both hardware and software capabilities. The hardware was designed to provide for flexibility across platforms and sensors. The software was designed within the *Simulink* environment in order to compliment the hardware. The software provides for both an autopilot hardware implementation template and an open source library. This chapter presents an overview of the autopilot hardware and the autopilot's *Simulink* software environment. In addition, a brief description of the templates, available library subsystems and how to implement them is provided.

#### 4.1 Hardware Overview

The autopilot hardware design included port connections for most standard hardware utilized on small scale unmanned systems. These include analog inputs, Transistor-Transistor Logic (TTL) and Input/Output (I/O), ports. In addition, the autopilot possesses pressure sensors for measuring altitude and forward velocity as well as Pulse Width Modulated (PWM) outputs for controlling standard servos. The three analog inputs have additional flexibility. A Field Programmable Analog Array (FPAA) was incorporated for customized signal conditioning development, which could be programmed into the FPAA from the FPGA. The TTL I/O ports provide for variable voltage settings through the use of a digital trim pot, which is also directly programmable

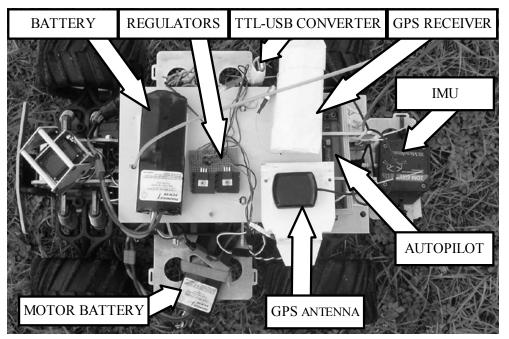

from the FPGA. The autopilot board developed and produced during this research is pictured in Figure 1.

Figure 1: Autopilot Board Overview

In order to both minimize size and provide custom analog and MEMS sensors to be developed for use with the autopilot, a stacked board design consisting of a main board and a secondary daughter board was implemented. The daughter board can be used for inclusion of application-specific hardware such as custom sensors. This is a necessary requirement for micro-air vehicles since the small payload capacity requires extremely small on-board sensors to be utilized.

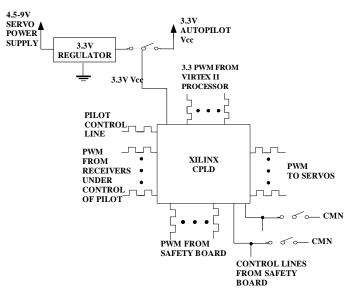

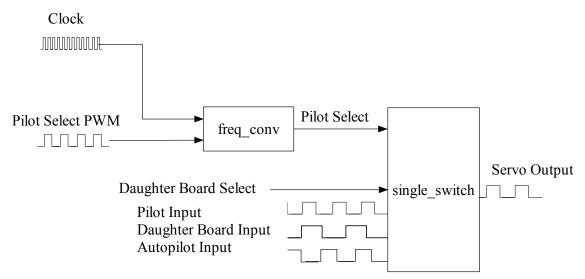

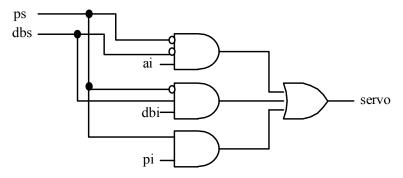

The FPGA outputs PWM logic to control servos through 3.3V TTL ports. The autopilot's servo connectors do not directly connect to the FPGA. The waveform is sent to the input ports through a Complex Programmable Logic Device (CPLD), which is used in the safety switch circuitry. This circuitry provides for connections from a handheld radio receiver for human pilot takeover. In addition, the circuitry also includes PWM and

select lines to the daughter board connectors to provide takeover capability from an external processing system. When a daughter board is not connected, jumpers are used to disable the second takeover option. While the safety switch was programmed for the behavior described, JTAG connectors are available on the back of the autopilot board. This provides for reprogramming of the CPLD in order to gain additional functionality. One additional pin has a direct connection to the FPGA in order to send information. This was provided as a tool to assist the programmer.

In addition to the hardware connectors, three user LEDs, one user switch, a power LED and a programming completed indicator were included on the board. These hardware assets provide indicators to assist the software developer and provide an additional logic input to the board. The hardware specifications for the autopilot developed and produced during this research is presented in Table 1.

Table 1: Autopilot Specifications

## I/0 ports and sensors

On-board pressure sensors for altitude and forward speed

Two large signal, single ended analog inputs

One small signal differential analog input

Twenty-Four variable voltage logic inputs

- Input voltage set in blocks of four

- 1.8V to 5V range

Four Tx and 5 Rx RS232 lines

Forty-Six 3.3V I/O FPGA connections to daughter board

#### Capabilities

On-board MicroSD card for data acquisition memory

A safety switch for servo control

Twelve servo outputs

- All twelve, selectable in sets of six by daughter board, (if present)

- Six critical servos, which can be taken over by a pilot

Simulink programming and hardware-in-the-loop capable

The board contains a Xilinx Spartan3-1400AN FPGA, which serves as the primary processing platform for the autopilot. By selecting from the Xilinx line of FPGAs, the autopilot was fully interfaced and integrated with *Simulink*. The reconfigurable nature of the FPGA provides the programming capabilities, which are necessary to compliment the flexibility of the hardware design. The hardware flexibility incorporates the handling of several types of communication protocol. The hardware accepts various ranges of analog sensor input and data acquisition. The hardware provides for measurement of altitude and forward speed through on-board pressure sensors. In addition, the hardware provides for releasing control of the servos to either a human pilot or a second processing system through the use of a daughter board.

### 4.2 Autopilot Software Environment

The user of the autopilot will have available, from within the *Simulink* environment, hardware protocol subsystems and the standard System Generator building blocks. In addition to the *Simulink*/System Generator software tools, the Xilinx's EDK environment can be utilized to develop soft core processors capable of running a user-selectable operating system. The overview of the autopilot's software environment is presented in Figure 2.

The available subsystem building blocks were developed specifically for the peripheral hardware contained on the autopilot. Other high level signal processing functions such as filtering, sensor integration and controllers can be developed using standard System Generator blocks. In addition, the soft core processors can contain a small operating system such as the Slackware version of Linux or VxWorks®. While this does seem contradictory to the argument for parallel processing, the ability to utilize

a DSP structure provides for the implementation of many algorithms, which have been developed to operate within a specific software environment, such as a wireless networking protocol. In addition, hardware may be designed into the system that utilizes Linux drivers without the additional work of developing custom software.

Figure 2: Software Block Diagram

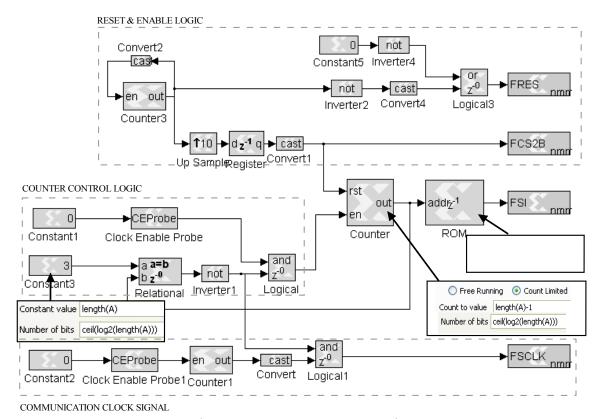

## **4.2.1** Hardware Co-Simulation Timing Issues

System Generator allows for hardware-in-the-loop simulation by compiling a co-simulation block that contains the bit stream for programming the FPGA and controls the JTAG communication. After the hardware co-simulation block is generated, it can be set to single stepping or free running by double-clicking the block. When single stepping is selected, *Simulink* controls the FPGA clock signal and the hardware matches the *Simulink* clock cycle, which does not relate to real-time. This is the preferable setting when communication with external hardware is not required. However, when the autopilot is to be programmed to interact with external hardware, real-time is required. The 'free running' selection will turn control of the clock over to the FPGA's 50MHz clock. Within the system there will be blocks, which must be synchronized by the system clock. When the System Generator blocks are converted to the FPGA hardware configuration bit stream, the resulting internal rates are related to the *Simulink* update rate. The update rate is provided by equation (1). This relationship was utilized within all the developed subsystems specifying hardware level timing.

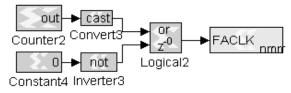

hardware update rate =

$$\frac{\text{Simulink update rate*hardware clock rate}}{\text{Simulink time step}}$$

(1)

A *Simulink* autopilot template was developed. The template contains masked subsystems to:

- program the FPAA,

- receive data from the A/D outputs from the FPAA,

- enable and receive data from the pressure sensors,

- initialize the MicroSD card,

- enable/disable the RS232 ports,

- enable/disable the variable I/O ports,

- set the desired voltage level

- generate the PWM outputs with selectable frequencies and duty cycles.

With the FPAA, the pressure sensors, all the PWM ports in use and the MicroSD card enabled the amount of slices utilized was 1362, or 12%. By disconnecting the outputs, connecting the PWM to logic low and deactivating the FPAA program subsystem, the unused logic is trimmed during hardware generation. Under these conditions the utilized slices are reduced to just 526, or 4%. The autopilot template is presented in Figure 3.

Figure 3: Autopilot Template

Several library subsystems were developed to accommodate both basic use of the on-board hardware and the communication requirements for the sensors utilized by the RC-Truck robot. The subsystems developed thus far include:

- an RS232 communication protocol,

- initialization the FPGA RAM for data acquisition,

- a communication protocol to receive latitude and longitude from the Superstar II GPS unit,

- a communication protocol to receive gyro-stabilized Euler angles from the MicroStrain IMU unit.

While the library is limited, the open source platform provides for continually increasing functionality as new software is developed over time by end users.

As a result of the pre-developed hardware level timing a variable declared as SimP, which defines the System Generator time step, must be specified by the end user. SimP can be defined either in the MATLAB workspace or the model explorer. Once defined, SimP is entered into the System Generator block. This provides for the simulation time step to be modified without affecting the final hardware level timing. The only restriction on the time step is that it must be less than 10usec. This restriction results from the communication protocol timing and the resolution of the generated PWM output. The System Generator block is presented in Figure 4.

Each of the template subsystems provided has a user interface, or mask, in order to enable/disable and select specific settings, with exception to A/D protocol of the FPAA. Since the FPAA is disabled through the programming subsystem, the outputs from the receive subsystem are left unconnected when not in use. When *Simulink*

generates the programming bit stream all the unconnected logic is removed and the inputs are ignored.

Figure 4: Simulink System Period Setting

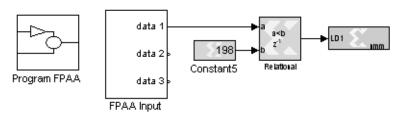

## **4.2.2** FPAA Programming and Utilization

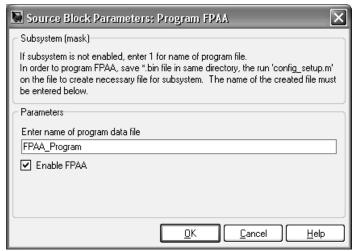

The FPAA subsystem program contained in the autopilot template allows the user to enable the system and enter the name of the workspace variable containing the FPAA program bit stream. Since the variable is entered into a *Simulink* block, in the underlying subsystem, the name must not be left empty. When the FPAA is not utilized, a value of '1' should be entered to prevent a *Simulink* error flag. When the 'Enable FPAA' is not selected the subsystem holds the outputs constant, which includes the clock signal to the FPAA. The FPAA program subsystem is presented in Figure 5.

Figure 5: FPAA Program Settings

The FPAA subsystem programs the FPAA from a variable, which must be created within the MATLAB workspace. This is accomplished by first generating a binary program file with Anadigm's AnadigmDesigner2 software. Once the binary file is created an m-file is utilized to read the file into a variable in the workspace. The m-code is used to create the necessary variable, *FPAA*, which is displayed in Figure 6.

```

1 - fid = fopen('FPAA.bin'); %config6.bin created by AnadigmDesigner2

2 - FPAA = fread(fid, 'ubit8'); % reads file into workspace

3 - FPAA=dec2bin(FPAA); % declares MATLAB variable containing binary values

4 - FPAA=reshape(FPAA',[],1); % reshapes variable to correct format

5 - FPAA=bin2dec(FPAA); % converts back to decimal so Similink can recognize

6 - FPAA=[FPAA; 1]; % add last one to stop output port on 'logic high'

```

Figure 6: FPAA Configuration M-File

The binary file is first read into MATLAB and then rearranged from an 8-bit word length to a 1-bit length. In order to reformat the word length, the '1's and '0's are declared as binary. After reshaping, they are re-declared as decimal values. The final step is to add a trailing one that is required to hold the output line high after the last bit is transmitted.

## 4.2.3 Utilizing Pressure Sensors for Altitude and Velocity

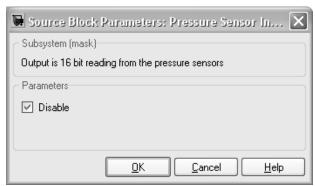

Two on-board pressure sensors were incorporated in the design of the autopilot platform. The pressure sensors provide for the measurement of altitude and forward velocity. The pressure sensors produce an analog signal, which is sent to a dual A/D converter. The template subsystem reads the two 16-bit values into the FPGA. The resolution of the calculations for altitude and velocity are user dependent. Therefore, logic was not created to convert altitude and velocity. In addition, the end user may wish to reduce the number of gates by implementing the 16-bit values directly in the controller algorithms. The subsystem contains a mask, which will disable the system by tying all the outputs to the A/D converter to logic high. The subsystem is presented in Figure 7.

Figure 7: Disabling Pressure Sensor

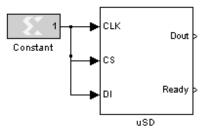

## 4.2.4 Initializing the MicroSD Card

Since there are many potential uses for the MicroSD card, the only logic included in the library is the sequence of instructions, which must be sent in order to initialize the card. The hardware ports were incorporated inside the template subsystem and can be accessed through the ports of the subsystem. When the card is not in use the input ports must be connected to a logic high constant. The card will still initialize but it will not

receive any further commands. When the card is in use the user must wait for logic high out of the *Ready* port before sending any commands. The output from the card is available through the *Dout* port. The MicroSD card is presented in Figure 8.

Figure 8: MicroSD Card Template Subsystem

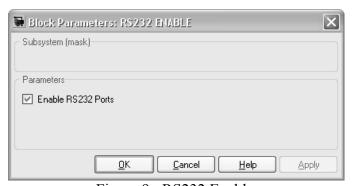

## 4.2.5 Disabling RS232 Ports

The RS232 ports can be enabled or disabled from within the template. The mechanism for manipulating RS232 enable is presented in Figure 9.

Figure 9: RS232 Enable

When disabled the FPGA output ports enabling the RS232 IC are held at logic low. This holds the I/O lines out of the autopilot at high impedance. When in use, the user can utilize the library blocks provided for the communication protocol.

## **4.2.6** Setting Variable Voltage I/O Ports

The template subsystem, which controls the variable I/O port settings, contains an enable and a voltage select available in six sets of four communication lines. The subsystem for I/O control is presented in Figure 10. When disabled, the voltage translator IC holds the autopilot I/O pins at high impedance. When enabled, the user can set the voltage to any of the predefined values of 1.8V, 3.3V or 5V.

Figure 10: Variable I/O Port Settings

# **4.2.7 Utilizing PWM Output Block**

The PWM template subsystem controls the generation of the signals to the 12 output ports. The output signals are generated by converting a duty cycle input, 0 to

100%, into the output square wave signal. Specification of a specific frequency between 20Hz and 100Hz, an initial duty cycle and specification of hardware or simulation timing, is user selectable. When simulation is selected the PWM frequency is matched to the simulation time steps. When hardware implementation is selected a conversion is included to set the PWM generated to the hardware clock. If the user sets the input to a constant of 100 the output lines are all held logic high. The PWM subsystem parameters are presented in Figure 11.

Figure 11: PWM Subsystem Settings

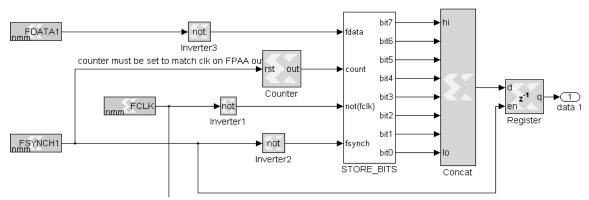

#### 4.2.8 RS232 Communication Subsystems

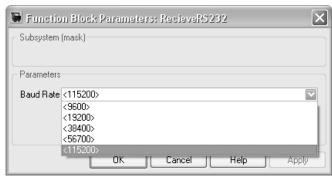

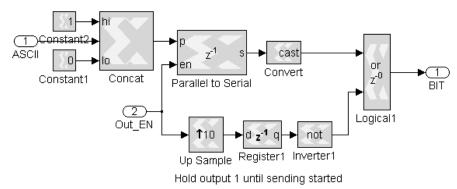

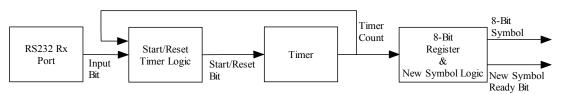

Separate library subsystems were developed for sending and receiving eight bit data with no parity and a stop bit of one. The receive function provide the user a capability to select from a list of baud rates, which includes 9600, 57600, 38400, 56200 and 115200 bps. The send function also provides for the same communication baud rates. However, the rate is set by the inputs to the subsystem.

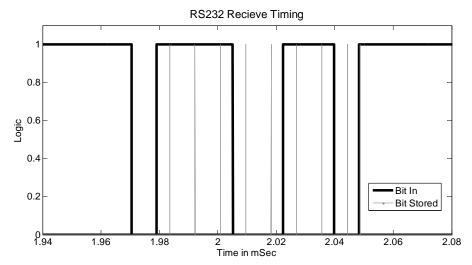

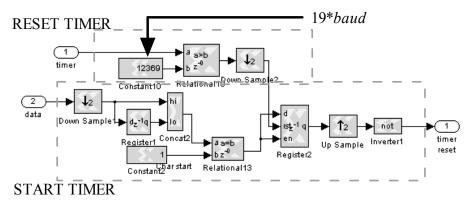

The receive subsystem over-samples the port at the clock frequency of the autopilot, which is 50MHz. This prevents an incoming byte from being misread due to clock drift or jitter. This works well for receiving data. However, it creates a very fast update rate within the System Generator. In some cases, where the incoming data is followed by only simple logic, this may not pose an issue. In other cases it sets up a timing requirement, which the hardware may not be able to meet. Therefore, a library subsystem was developed, which down-samples the output to the actual baud rate.

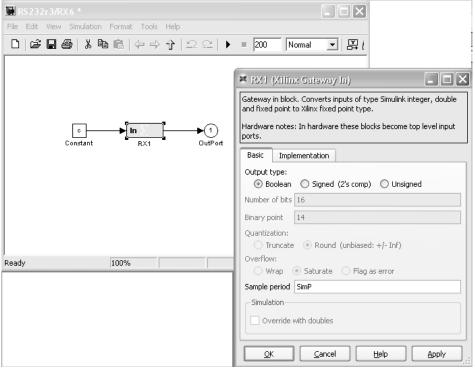

The library subsystem that receives the RS232 data from the I/O port has one input and two output ports. The input is the autopilot hardware port, which receives the bit level input and must be set to the clock rate under the mask. Entering the variable *SimP* will make the necessary clock adjustment for a rate of 20ns. This process is presented in Figure 12.

The two outputs from the subsystem consist of the received 8-bit character and a 1-bit flag. The 1-bit flag is held logic high for one clock cycle when a new character has been received. The baud rate is set with the drop-down menu as demonstrated in Figure 13

Figure 12: Setting Input Port Timing

Figure 13: Setting Baud Rate

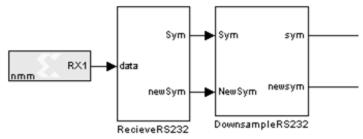

The down-sample RS232 library subsystem has two inputs and two outputs, which correspond to the outputs of the subsystem receiving the RS232 data. The 8-bit received data and the flag from the receive RS232 block are down-sampled to the selected baud rate and passed out of the function. The output rate is selected by the same style of drop-down menu as the receive subsystem. This process is presented in Figure 14.

Figure 14: RS232 Down-Sample

The RS232 library subsystem, which sends the 8-bit data, has two inputs and one output port. The first input port, termed *ascii*, holds the 8-bit character to be sent. The second, termed *Out\_EN*, holds a logic in, which sends the character when equal to one. The inputs set the rate of the blocks contained within the subsystem and must correspond correctly to the selected baud rate. The output port, termed *BIT*, is connected to the selected hardware port. This includes the RS232 ports and the variable level logic ports, which can be used with TTL to USB converters for receipt of the RS232 protocol. The settings are listed in Table 2.

Table 2: RS232 Send Input Timing

| Baud Rate, Bits Per Second | Input Rate, Seconds |  |  |  |

|----------------------------|---------------------|--|--|--|

| 1900                       | $1.042(10^3)$       |  |  |  |

| 19,200                     | $5.208(10^4)$       |  |  |  |

| 34,800                     | $2.604(10^4)$       |  |  |  |

| 56,700                     | $1.736(10^4)$       |  |  |  |

| 115,200                    | 8.68(105)           |  |  |  |

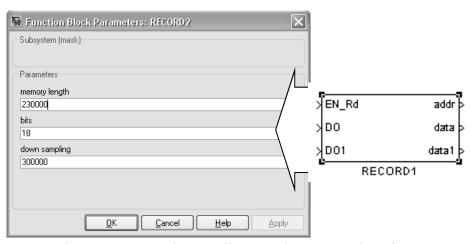

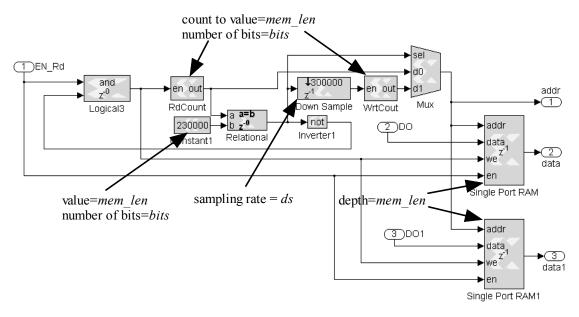

## 4.2.9 FPGA RAM Data Acquisition Library Block

When developing the correct logic design for communicating with external hardware the testing of the protocol must be performed with the co-simulation block set to free running. This setting will insure that the hardware timing is implemented

correctly. Since the update of the JTAG port is much slower than any standard communication rate, this prevents hardware-in-the-loop verification from being utilized. This library subsystem was developed as a solution to that issue. Values occurring within the FPGA are stored within RAM memory. When the memory is full the values are sent to the JTAG port at a rate, which is more acceptable. The rate must be determined by the end user. This is due to the fact that longer word lengths require more time to receive. Once the data has been received through the JTAG port, the values can be graphed by any MATLAB method for analysis.

The library subsystem allows for two inputs to be recorded and also includes an enable port so that the data can be saved at a specific time. The outputs from the subsystem are each connected to a JTAG System Generator block, termed Gateway Out. These outputs are the address, *addr*, and the two recorded strings of data, *data* and *data1*. These outputs are presented in Figure 15.

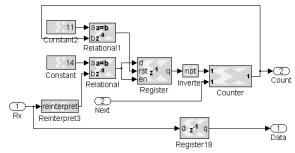

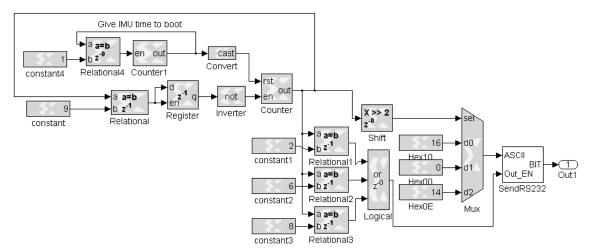

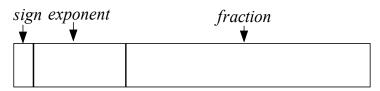

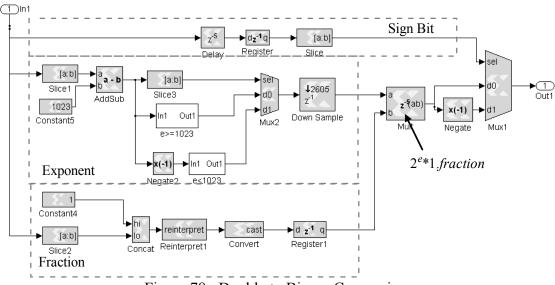

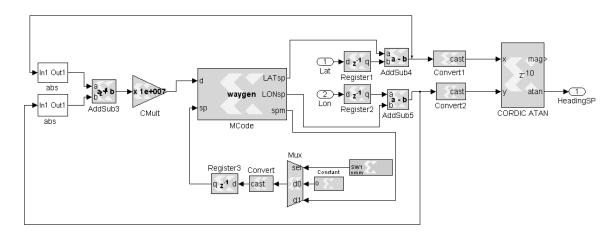

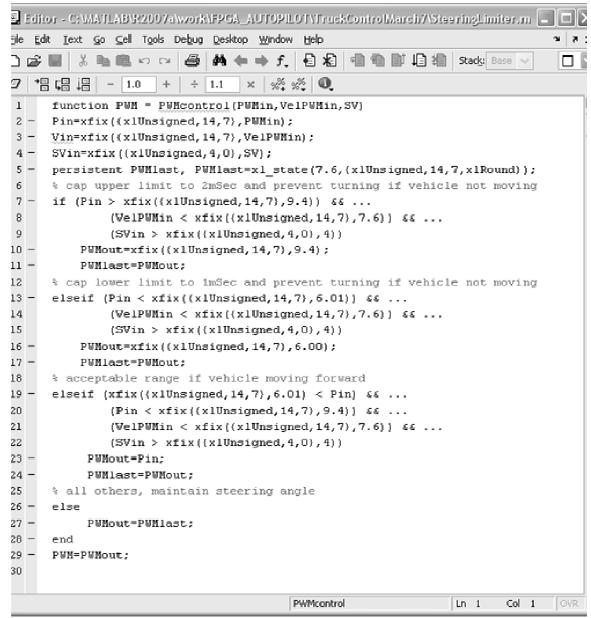

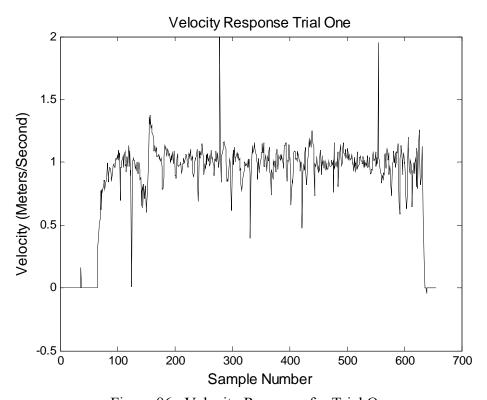

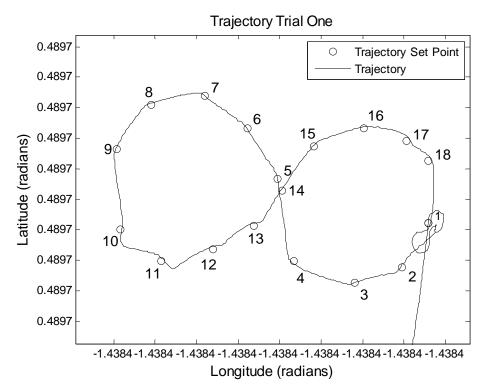

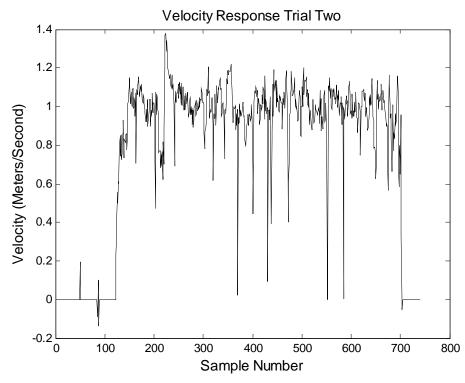

Figure 15: Record Data Library Subsystem and Settings